# **MÓDULO 8810**

## MANUAL TÉORICO E PRÁTICO

## **MÓDULO 8810**

## MANUAL TEÓRICO E PRÁTICO

## **SUMÁRIO**

| <u>CAPÍ</u> | TULO 1 – GATES LÓGICOS BÁSICOS            | 1  |

|-------------|-------------------------------------------|----|

| 1.1         | FUNÇÃO LÓGICA GATES "E" (AND)             | 1  |

| 1.1.1       | RESUMO                                    | 1  |

| 1.1.2       | OBJETIVO                                  | 1  |

| 1.1.3       | EXPERIÊNCIA 1                             | 1  |

| 1.1.4       | EXPERIÊNCIA 2                             | 3  |

| 1.1.5       | DEMORA DE PROPAGAÇÃO (DELAY TIME)         | 4  |

| 1.1.6       | EXERCÍCIOS                                | 6  |

| 1.2         | FUNÇÃO LÓGICA GATE "OU" (OR)              | 7  |

| 1.2.1       | RESUMO                                    | 7  |

| 1.2.2       | OBJETIVO                                  | 7  |

| 1.2.3       | EXPERIÊNCIA 3                             | 7  |

| 1.2.4       | EXPERIÊNCIA 4                             | 8  |

| 1.2.5       | EXPERIÊNCIA 5                             | 9  |

| 1.2.6       | ANÁLISE DE DEMORA                         | 11 |

| 1.2.7       | EXERCÍCIOS                                | 12 |

| 1.3         | FUNÇÃO LÓGICA GATE "NÃO" (INVERSOR) (NOT) | 13 |

| 1.3.1       | RESUMO                                    | 13 |

| 1.3.2       | OBJETIVO                                  | 13 |

| 1.3.3       | EXPERIÊNCIA 6                             | 13 |

| 1.3.4       | EXERCÍCIOS                                | 16 |

| 1.4         | FUNÇÃO LÓGICA GATE "NÃO-E" (NAND)         | 17 |

| 1.4.1       | RESUMO                                    | 17 |

| 1.4.2       | OBJETIVO                                  | 17 |

| 1.4.3       | EXPERIÊNCIA 7                             | 17 |

| 1.4.4       | EXPERIÊNCIA 8                             | 19 |

| 1.4.5       | EXPERIÊNCIA 9                             | 20 |

| 1.4.6 | EXPERIÊNCIA 10                          | 21 |

|-------|-----------------------------------------|----|

| 1.4.7 | EXPERIÊNCIA 11                          | 22 |

| 1.4.8 | EXERCÍCIOS                              | 23 |

| 1.5   | FUNÇÃO LÓGICA GATE "NÃO-OU" (NOR)       | 24 |

| 1.5.1 | RESUMO                                  | 24 |

| 1.5.2 | OBJETIVO                                | 24 |

| 1.5.3 | EXPERIÊNCIA 12                          | 24 |

| 1.5.4 | EXPERIÊNCIA 13                          | 26 |

| 1.5.5 | EXPERIÊNCIA 14                          | 26 |

| 1.5.6 | EXPERIÊNCIA 15                          | 28 |

| 1.5.7 | EXPERIÊNCIA 16                          | 28 |

| 1.5.8 | EXPERIÊNCIA 17                          | 29 |

| 1.5.9 | EXERCÍCIOS                              | 31 |

| 1.6   | FUNÇÃO LÓGICA GATE "OU-EXCLUSIVO" (XOR) | 32 |

| 1.6.1 | RESUMO                                  | 32 |

| 1.6.2 | OBJETIVO                                | 32 |

| 1.6.3 | EXPERIÊNCIA 18                          | 32 |

| 1.6.4 | EXPERIÊNCIA 19                          | 33 |

| 1.6.5 | EXPERIÊNCIA 20                          | 34 |

| 1.6.6 | EXPERIÊNCIA 21                          | 35 |

| 1.6.7 | EXERCÍCIOS                              | 37 |

| 1.7   | TEOREMA DE "DE MORGAN"                  | 38 |

| 1.7.1 | RESUMO                                  | 38 |

| 1.7.2 | EXPERIÊNCIA 22                          | 38 |

| 1.7.3 |                                         | 39 |

| 1.7.4 | EXPERIÊNCIA 24                          | 41 |

| 1.7.5 | EXERCÍCIOS                              | 44 |

| 1.8   | GATES DE COLETOR ABERTO                 | 45 |

| 1.8.1 | RESUMO                                  | 45 |

| 1.8.2       | EXPERIÊNCIA 25                                | 46 |

|-------------|-----------------------------------------------|----|

| 1.8.3       | EXPERIÊNCIA 26                                | 47 |

| 1.8.4       | EXERCÍCIOS                                    | 49 |

| 1.9         | GATES TRI-STATE                               | 50 |

| 1.9.1       | RESUMO                                        | 50 |

| 1.9.2       | EXPERIÊNCIA 27                                | 51 |

| 1.9.3       | EXPERIÊNCIA 28                                | 52 |

| 1.9.4       | EXERCÍCIOS                                    | 54 |

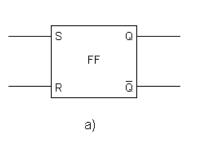

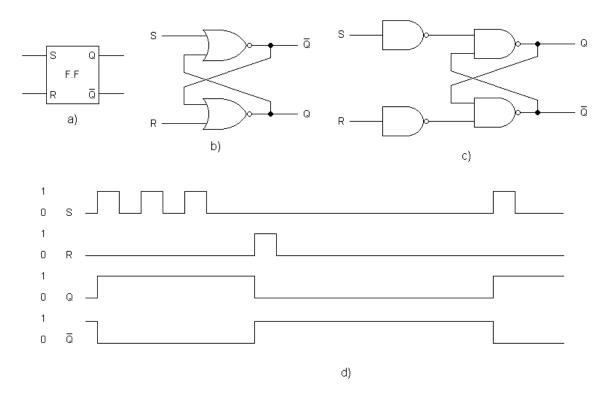

| <u>CAPÍ</u> | TULO 2 – FLIP FLOPS                           | 55 |

| 2.1         | RESUMO                                        | 55 |

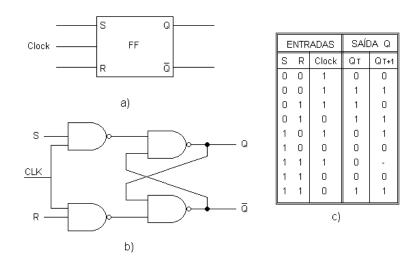

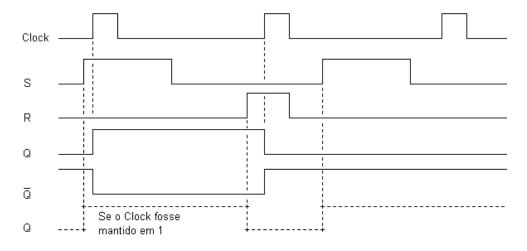

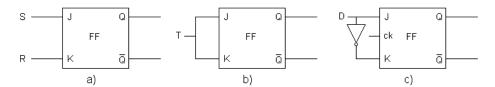

| 2.2         | FLIP-FLOP S-R                                 | 55 |

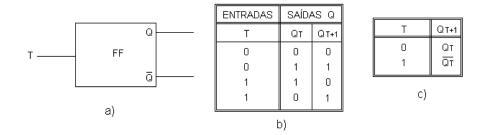

| 2.3         | FLIP-FLOP T                                   | 58 |

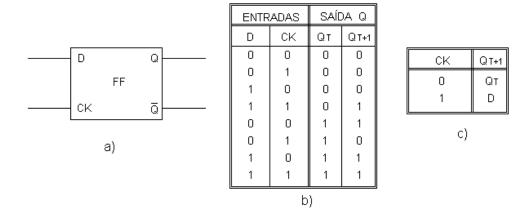

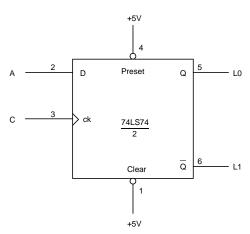

| 2.4         | FLIP-FLOP D                                   | 58 |

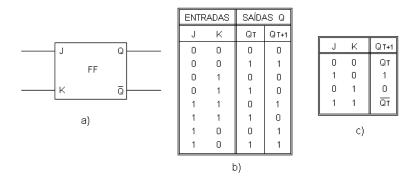

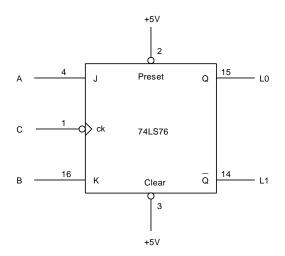

| 2.5         | FLIP-FLOP JK                                  | 59 |

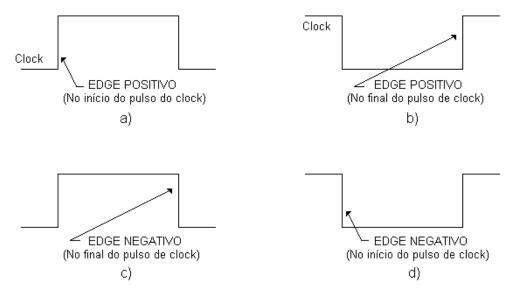

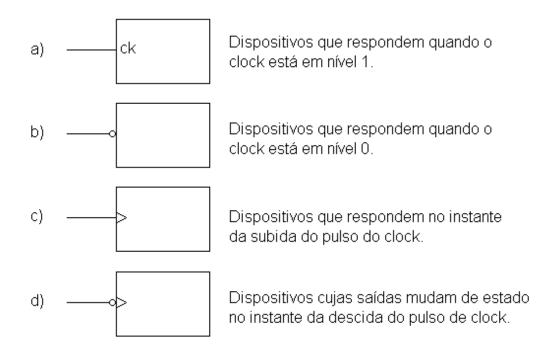

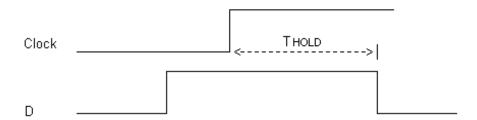

| 2.6         | TIPOS DE GATILHAMENTO DOS FLIP-FLOPS          | 59 |

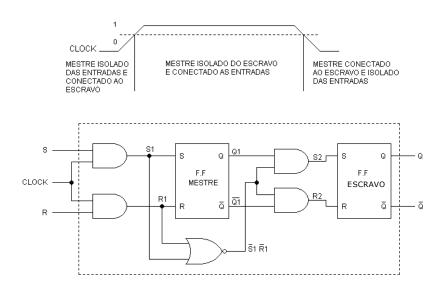

| 2.7         | FLIP-FLOPS GATILHÁVEIS DO TIPO MESTRE-ESCRAVO | 61 |

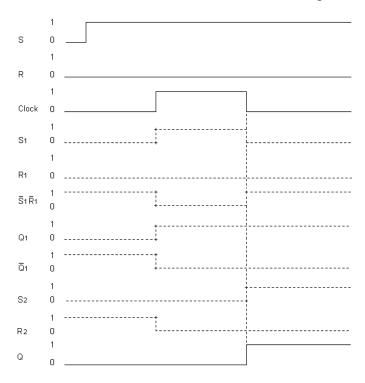

| 2.7.1       | FLIP-FLOP MESTRE-ESCRAVO COM DATA LOCK-OUT    | 63 |

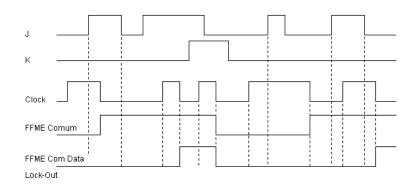

| 2.8         | PARÂMETROS IMPORTANTES DOS FLIP-FLOPS         | 63 |

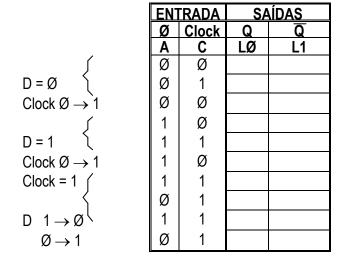

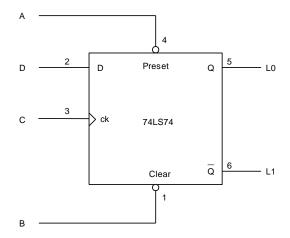

| 2.9         | EXPERIÊNCIA 1                                 | 64 |

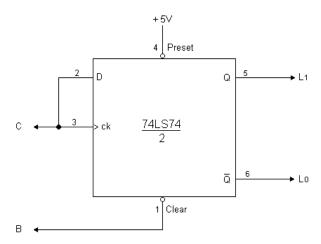

| 2.10        | EXPERIÊNCIA 2                                 | 65 |

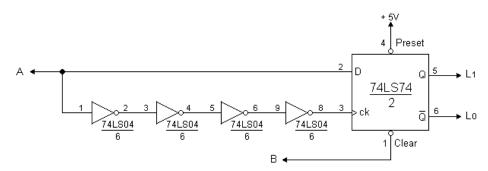

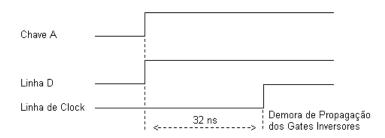

| 2.11        | EXPERIÊNCIA 3                                 | 67 |

| 2.12        | EXPERIÊNCIA 4                                 | 68 |

| 2.13        | EXERCÍCIOS                                    | 70 |

| <u>CAPÍ</u> | TULO 3 - CONTADORES                           | 71 |

| 3.1         | DEFINIÇÃO                                     | 71 |

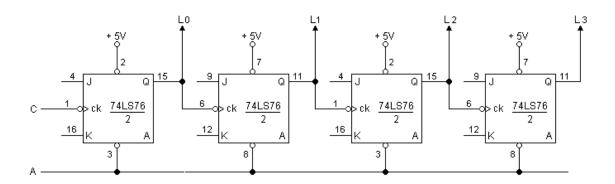

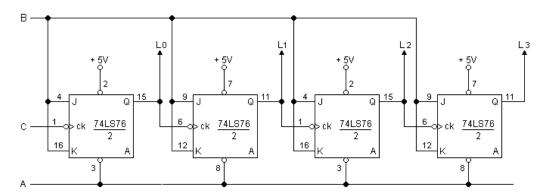

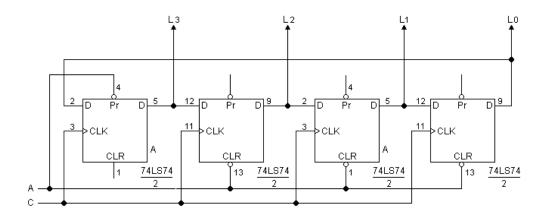

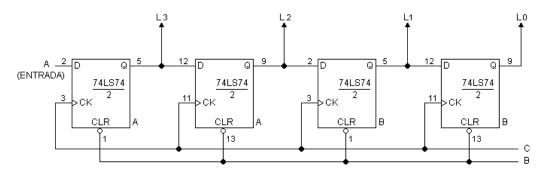

| 3.2         | CONTADORES RIPPLE (ASSINCRONO)                | 71 |

| 3.2.1       | EXPERIÊNCIA 1                                 | 71 |

|             |                                               |    |

| 3.2.2       | EXPERIÊNCIA 2                      | 73  |

|-------------|------------------------------------|-----|

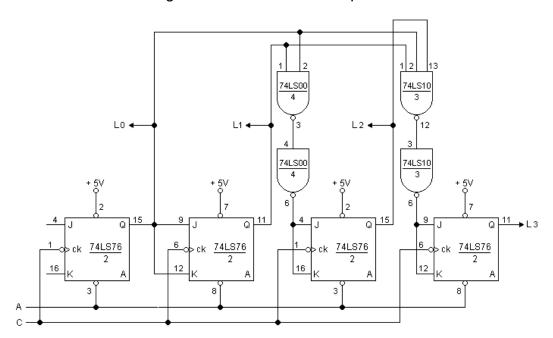

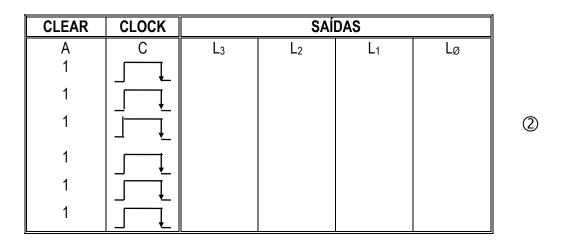

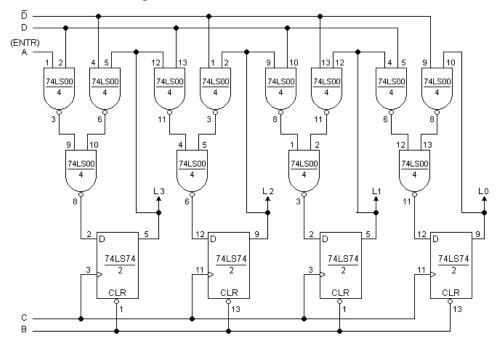

| 3.3         | CONTADORES SÍNCRONOS               | 74  |

| 3.3.1.      | EXPERIÊNCIA 3                      | 74  |

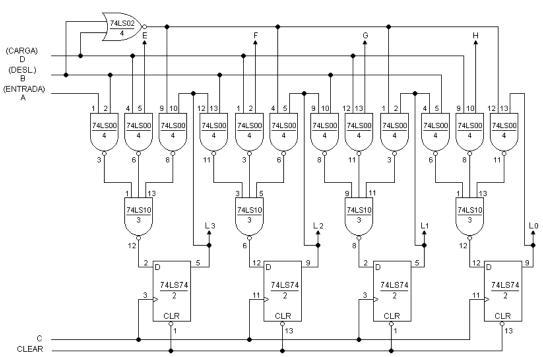

| 3.4         | CONTADORES SÍNCRONOS CONTROLADOS   | 76  |

| 3.5         | CONTADORES EM ANEL                 | 76  |

| 3.5.1       | EXPERIÊNCIA 4                      | 76  |

| 3.6         | CONTADORES NA FORMA DE CI's        | 78  |

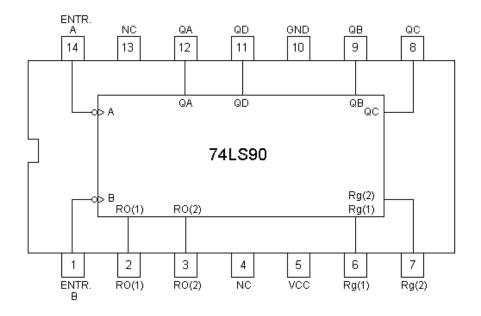

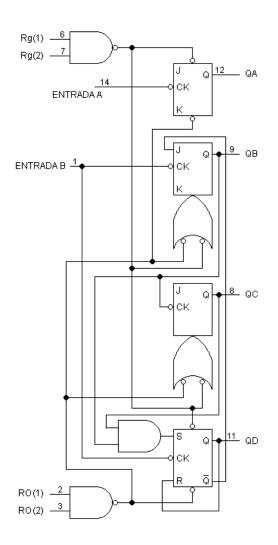

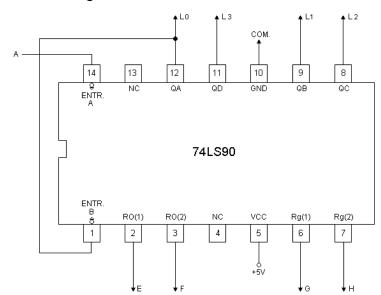

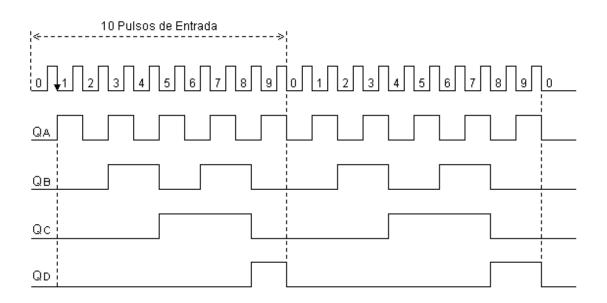

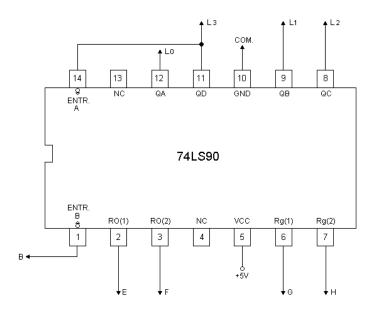

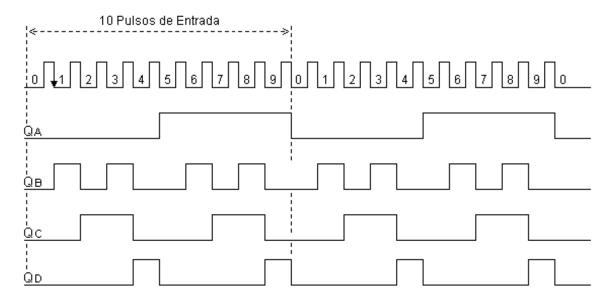

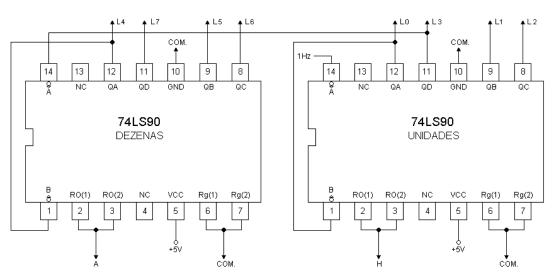

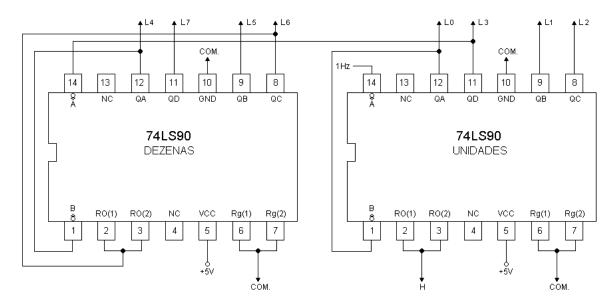

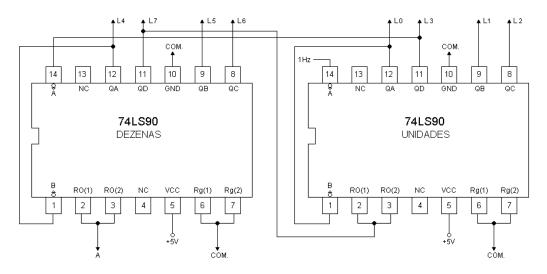

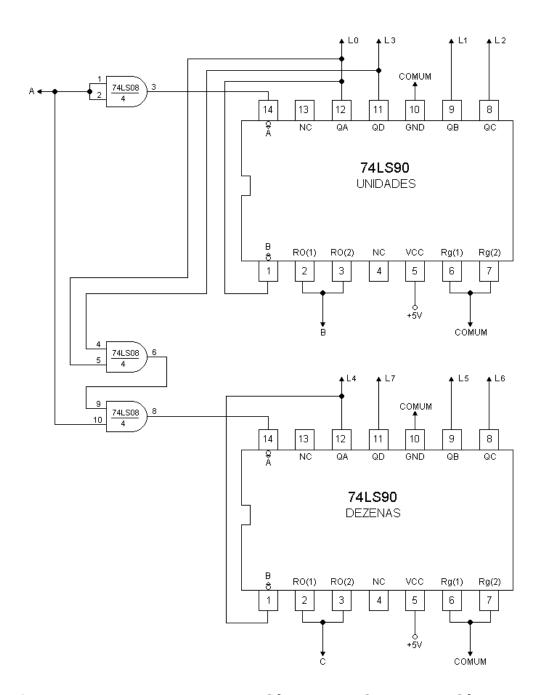

| 3.6.1       | CONTADOR 74LS90                    | 78  |

| 3.6.1.      | 1 EXPERIÊNCIA 5                    | 80  |

| 3.6.1.      | 2 EXPERIÊNCIA 6                    | 82  |

| 3.6.1.      | 3 LIGAÇÃO DE CONTADORES EM CASCATA | 84  |

| 3.6.1.      | 4 EXPERIÊNCIA 7                    | 84  |

| 3.6.1.      | 5 EXPERIÊNCIA 8                    | 86  |

| 3.6.1.      | 6 EXPERIÊNCIA 9                    | 88  |

| 3.6.1.      | 7 EXPERIÊNCIA 10                   | 89  |

| 3.6.1.      | 8 EXPERIÊNCIA 11                   | 91  |

| <u>CAPÍ</u> | TULO 4 - REGISTRADORES             | 95  |

| 4.1         | RESUMO                             | 95  |

| 4.2         | REGISTRADORES BUFFER               | 95  |

| 4.2.1       | EXPERIÊNCIA 1                      | 95  |

| 4.2.2       | EXPERIÊNCIA 2                      | 96  |

| 4.3         | REGISTRADORES DE DESLOCAMENTO      | 98  |

| 4.3.1       | EXPERIÊNCIA 3                      | 98  |

| 4.3.2       | EXPERIÊNCIA 4                      | 99  |

| 4.3.3       | EXPERIÊNCIA 5                      | 100 |

| 4.4         | CARREGAMENTO PARALELO              | 101 |

| 4.4.1       | EXPERIÊNCIA 6: (OPCIONAL)          | 101 |

| 4.5         | REGISTRADORES NA FORMA DE CI's     | 103 |

|             |                                    |     |

| <u>CAPÍ</u> | TULO 5 - DECODIFICADORES                                  | 105           |

|-------------|-----------------------------------------------------------|---------------|

| 5.1         | RESUMO                                                    | 105           |

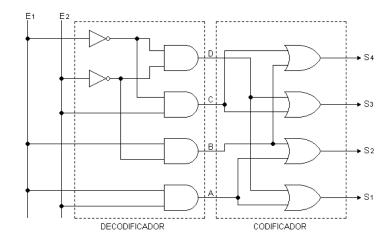

| 5.2         | EXPERIÊNCIA 1                                             | 106           |

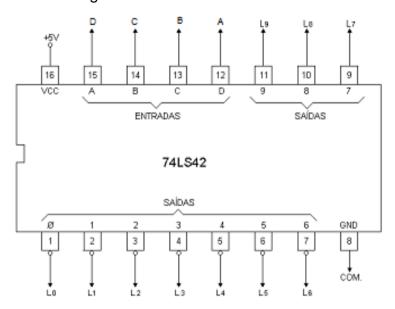

| 5.3         | DECODIFICADOR BCD PARA DECIMAL                            | 106           |

| 5.3.1       | EXPERIÊNCIA 2                                             | 107           |

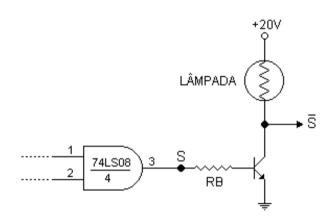

| 5.4         | DECODIFICADOR DRIVER                                      | 108           |

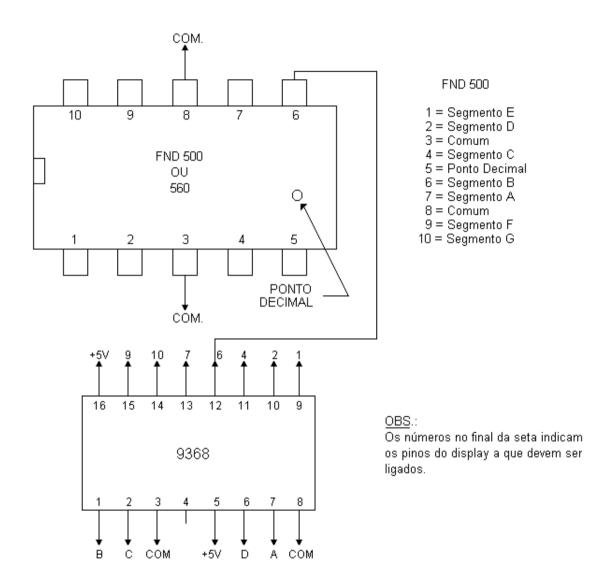

| 5.4.1       | DECODIFICADOR/DRIVERS BCD PARA 7 SEGMENTOS                | 109           |

| 5.4.1.      | .1 EXPERIÊNCIA 3                                          | 110           |

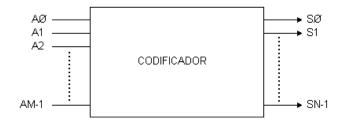

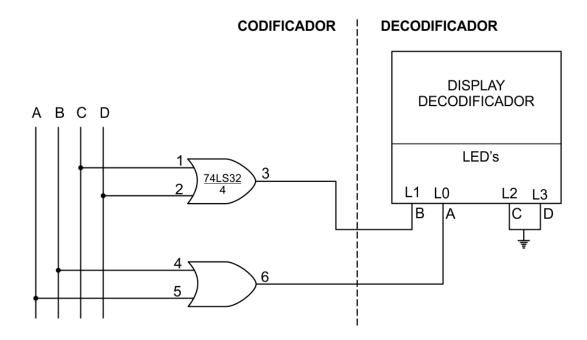

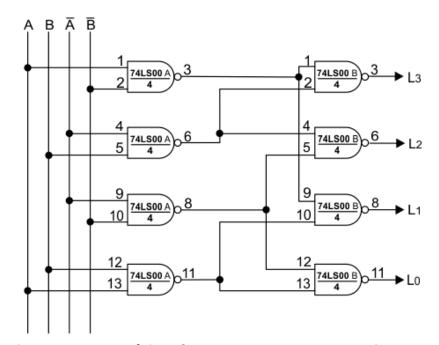

| <u>CAPÍ</u> | TULO 6 - CODIFICADORES                                    | 113           |

| 6.1         | RESUMO                                                    | 113           |

| 6.2         | EXPERIÊNCIA 1                                             | 113           |

| 6.3         | EXPERIÊNCIA 2                                             | 114           |

| 6.4         | CHAVES CODIFICADORAS                                      | 115           |

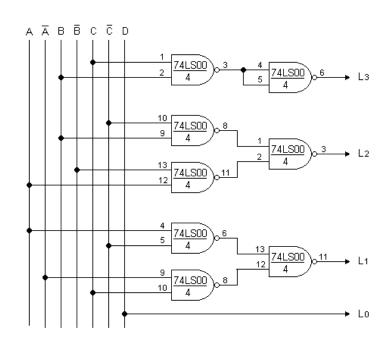

| 6.5         | CONVERSORES DE CÓDIGOS                                    | 116           |

| 6.5.1       | EXPERIÊNCIA 3                                             | 116           |

| <u>CAPÍ</u> | TULO 7 - MULTIPLEXADORES                                  | 119           |

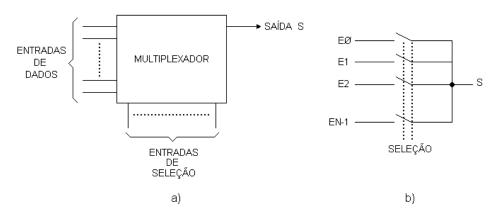

| 7.1         | RESUMO                                                    | 119           |

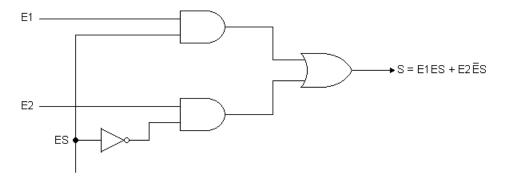

| 7.2         | MULTIPLEXADOR DE 2 ENTRADAS                               | 119           |

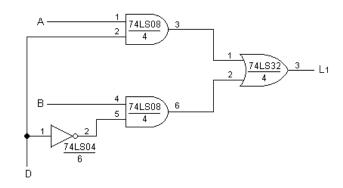

| 7.2.1       | EXPERIÊNCIA 1                                             | 120           |

| 7.3         | MULTIPLEXADORES NA FORMA DE CI'S                          | 121           |

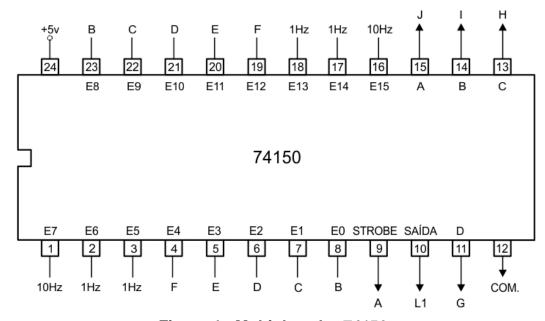

| 7.3.1       | EXPERIÊNCIA 2                                             | 121           |

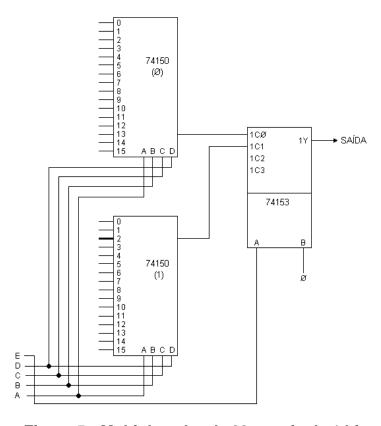

| 7.4         | USO DE CI'S MULTIPLEXADORES PARA FORMAR MULTIPLEX MAIORES | ADORES<br>123 |

|             |                                                           |               |

| <u>CAPÍ</u> | TULO 8 - DEMULTIPLEXADORES                                | 125           |

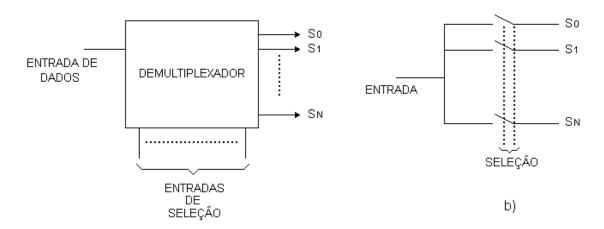

| 8.1         | RESUMO                                                    | 125           |

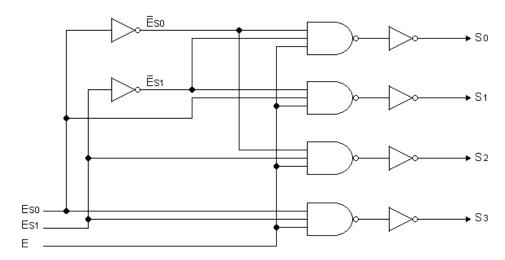

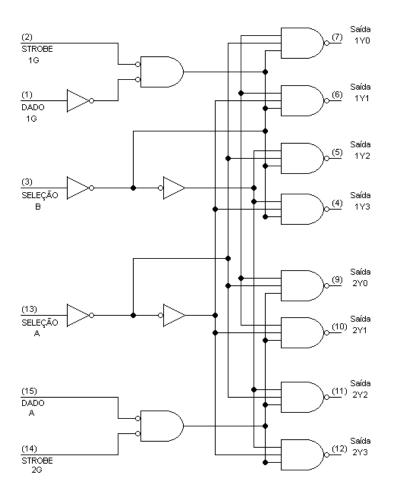

| 8.2         | DEMULTIPLEXADOR DE 4 SAÍDAS                               | 126           |

| 8.2.1       | EXPERIÊNCIA 1                                             | 126           |

|             |                                                           |               |

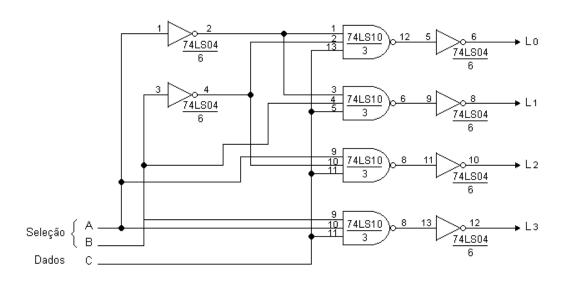

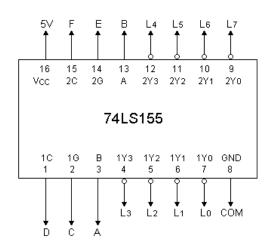

| 8.3         | DEMULTIPLEXADORES NA FORMA DE CI's                     | 127 |

|-------------|--------------------------------------------------------|-----|

| 8.3.1       | DEMULTIPLEXADOR 74LS155                                | 127 |

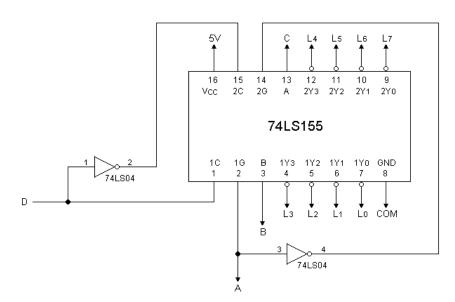

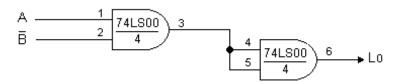

| 8.3.1.      | 1 EXPERIÊNCIA 2                                        | 128 |

| 8.3.1.      | 2 EXPERIÊNCIA 3                                        | 130 |

|             |                                                        |     |

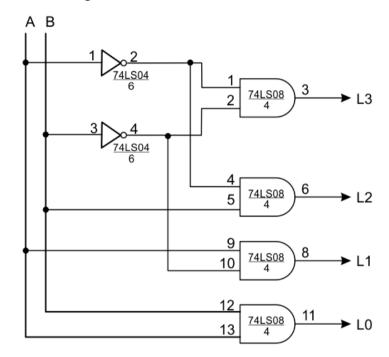

| <u>CAPÍ</u> | TULO 9 - COMPARADORES DIGITAIS                         | 133 |

| 9.1         | RESUMO                                                 | 133 |

| 9.2         | EXPERIÊNCIA 1                                          | 133 |

| 9.3         | EXPERIÊNCIA 2                                          | 134 |

| 9.4         | EXPERIÊNCIA 3                                          | 134 |

| 9.5         | EXPERIÊNCIA 4                                          | 135 |

| 9.6         | EXPERIÊNCIA 5                                          | 136 |

| 9.7         | EXPERIÊNCIA 6                                          | 136 |

| 9.8         | COMPARADOR DE MAGNITUDE NA FORMA DE CI                 | 137 |

| 9.8.1       | RESUMO                                                 | 137 |

| 9.8.2       | EXPERIÊNCIA 7                                          | 138 |

| 9.9         | COMPARADORES MAIORES COM O 74LS85                      | 140 |

|             |                                                        |     |

| <u>CAPÍ</u> | TULO 10 - GERAÇÃO E CHECK DE PARIDADE                  | 143 |

| 10.1        | RESUMO                                                 | 143 |

| 10.2        | CHEQUE DE PARIDADE                                     | 144 |

| 10.2.1      | EXPERIÊNCIA 1                                          | 145 |

| 10.3        | GERAÇÃO DE PARIDADE                                    | 145 |

| 10.3.1      | EXPERIÊNCIA 2                                          | 146 |

| 10.4        | CIRCUITOS INTEGRADOS PARA CHEQUE E GERAÇÃO DE PARIDADE | 147 |

| 10.4.1      | EXPERIÊNCIA 3                                          | 147 |

| 10.5        | USO DO 74LS180 PARA CHEQUE DE PARIDADE DE 9 BITS       | 149 |

| 10.5.1      | EXPERIÊNCIA 4                                          | 149 |

| 10.6        | USO DO 74LS180 EM CASCATA                              | 150 |

| <u>CAPÍTU</u> | ILO 11 - CIRCUITOS ARITMÉTICOS                        | 151 |

|---------------|-------------------------------------------------------|-----|

| 11.1 R        | ESUMO                                                 | 151 |

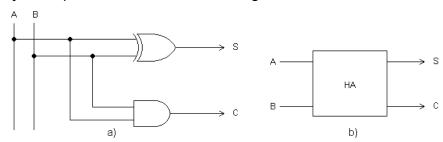

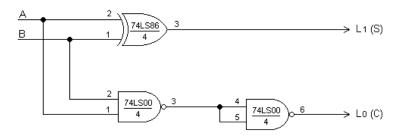

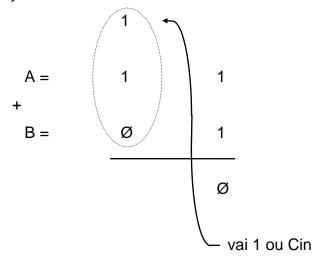

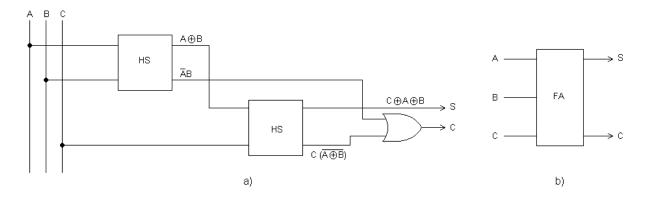

| 11.2 N        | IEIO SOMADOR                                          | 151 |

| 11.2.1        | EXPERIÊNCIA 1                                         | 152 |

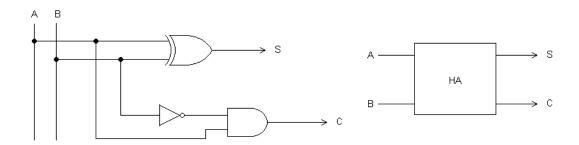

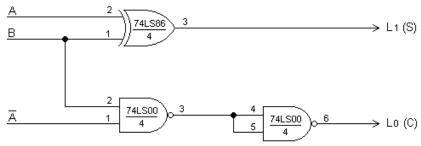

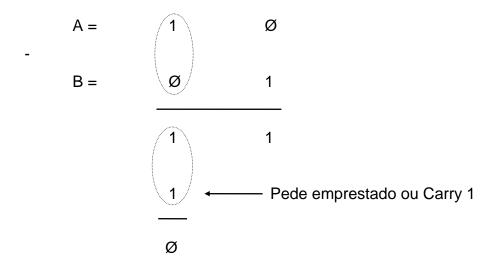

| 11.3 N        | IEIO SUBTRATOR                                        | 152 |

| 11.3.1        | EXPERIÊNCIA 2                                         | 153 |

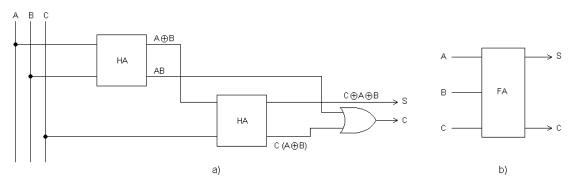

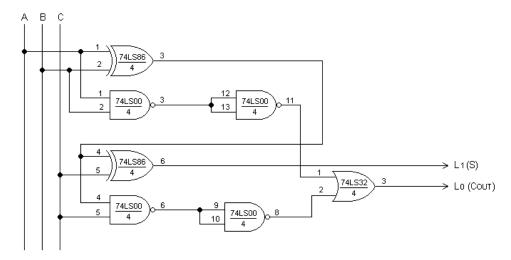

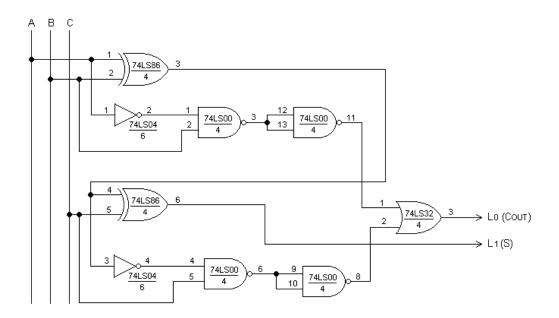

| 11.4 S        | OMADOR                                                | 154 |

| 11.4.1        | EXPERIÊNCIA 3                                         | 155 |

| 11.5 S        | UBTRATOR                                              | 156 |

| 11.5.1        | EXPERIÊNCIA 4                                         | 158 |

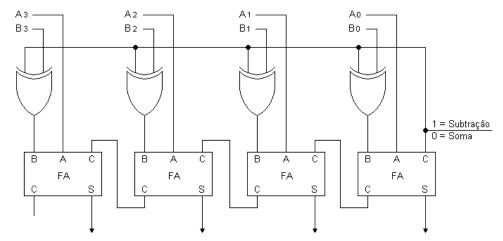

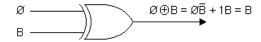

| 11.6 S        | UBTRAÇÃO ATRAVÉS DE SOMA                              | 159 |

| 11.6.1        | COMPLEMENTO DE UM NÚMERO BINÁRIO                      | 159 |

| 11.6.2        | COMPLEMENTO DE DOIS DE UM NÚMERO BINÁRIO              | 159 |

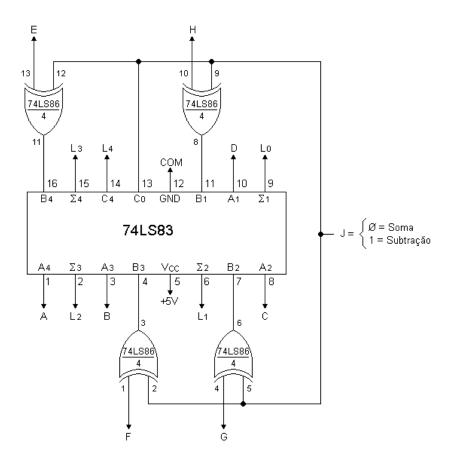

| 11.6.3        | CIRCUITO SUBTRATOR SOMADOR                            | 160 |

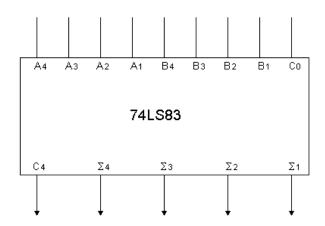

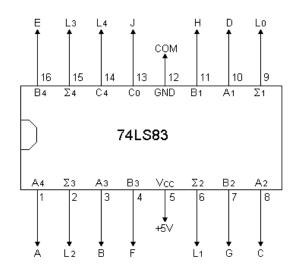

| 11.7 S        | OMADORES PARALELOS NA FORMA DE CI'S                   | 162 |

| 11.7.1        | EXPERIÊNCIA 5                                         | 162 |

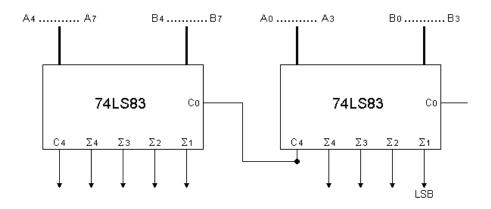

| 11.8 L        | IGAÇÃO DE SOMADORES CI'S PARALELOS EM CASCATA         | 163 |

| 11.8.1        | EXPERIÊNCIA 6                                         | 164 |

| 11.8.2        | EXPERIÊNCIA 7                                         | 165 |

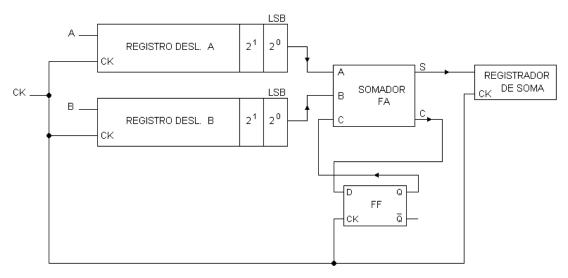

| 11.9 S        | OMADOR SÉRIE                                          | 166 |

| 11.9.1        | FUNCIONAMENTO DO SOMADOR SÉRIE                        | 167 |

| 11.10 O       | VERFLOW E UNDERFLOW NA ARITMÉTICA DO COMPLEMENTO DE 2 | 167 |

| 11.10.1       | OVERFLOW E UNDERFLOW NA ADIÇÃO                        | 168 |

| 11.10.2       | OVERFLOW E UNDERFLOW NA SUBTRAÇÃO                     | 168 |

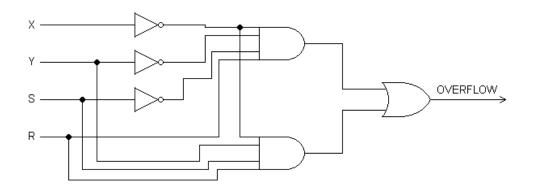

| 11.10.3       | DETEÇÃO DE OVERFLOW E UNDERFLOW                       | 169 |

| 11.10.4       | EXPERIÊNCIA 8                                         | 170 |

| 11.11 A       | RITMÉTICA BCD                                         | 171 |

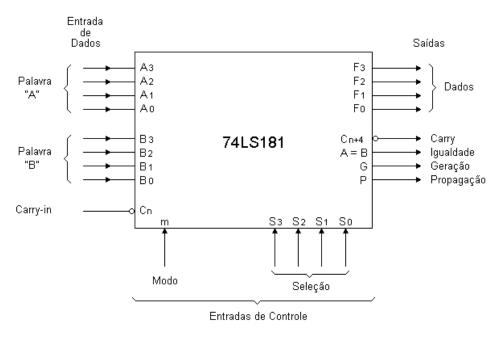

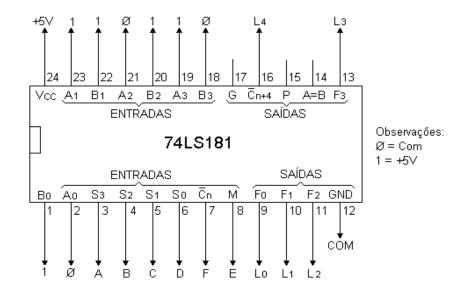

| CAPÍTULO 12 - UNIDADES ARITMÉTICAS E LÓGICAS (ALU's) | 173 |

|------------------------------------------------------|-----|

| 12.1 RESUMO                                          | 173 |

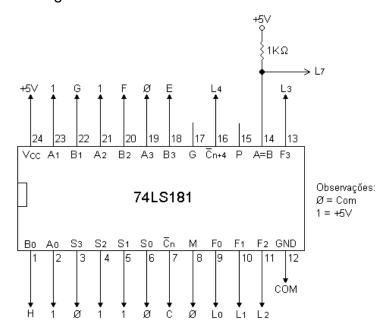

| 12.2 O 74LS181                                       | 173 |

| 12.2.1 EXPERIÊNCIA 1                                 | 175 |

| 12.3 USO DO COMPARADOR DO 74LS181                    | 176 |

| 12.3.1 EXPERIÊNCIA 2                                 | 177 |

| CAPÍTULO 13 - MONOESTÁVEIS E ASTÁVEIS                | 179 |

| 13.1 INTRODUÇÃO                                      | 179 |

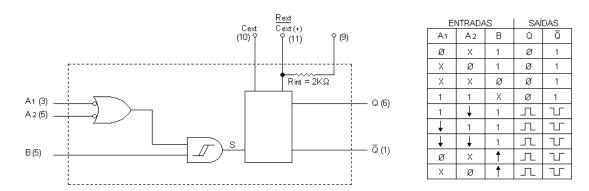

| 13.2 MONOESTÁVEIS COM CI's                           | 180 |

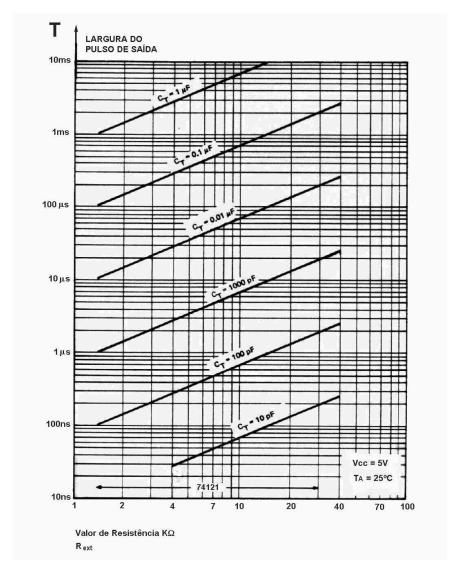

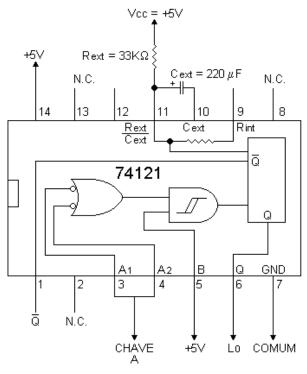

| 13.2.1 O 74121                                       | 180 |

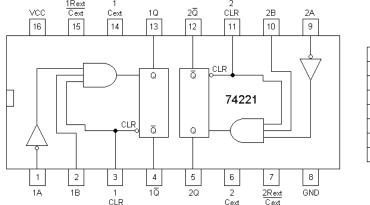

| 13.2.2 O 74221                                       | 182 |

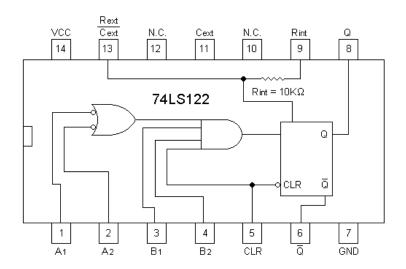

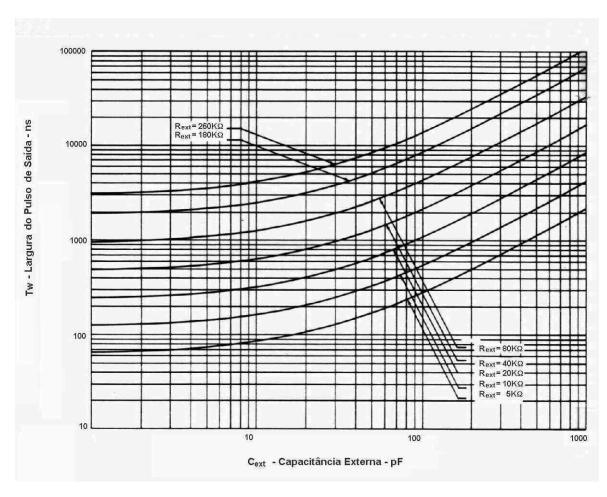

| 13.2.3 O 74LS122                                     | 183 |

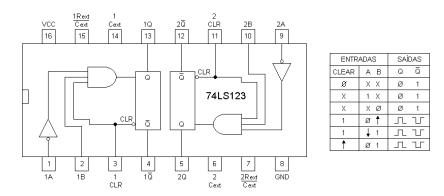

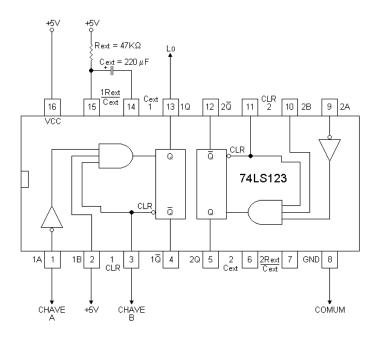

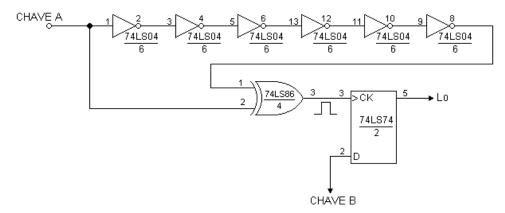

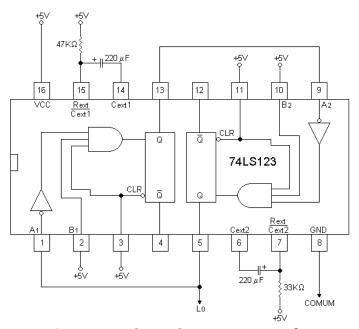

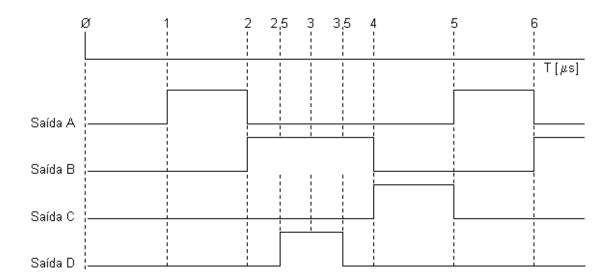

| 13.2.4 O 74LS123                                     | 184 |

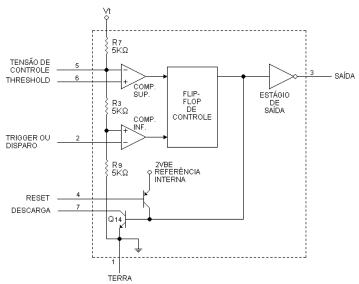

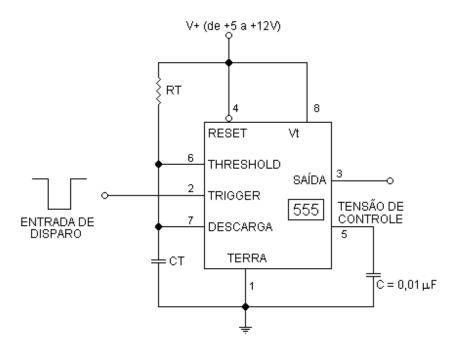

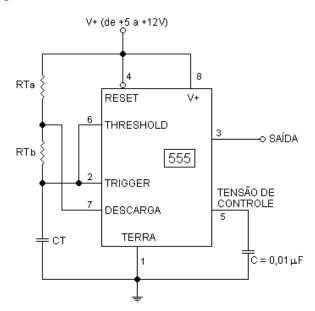

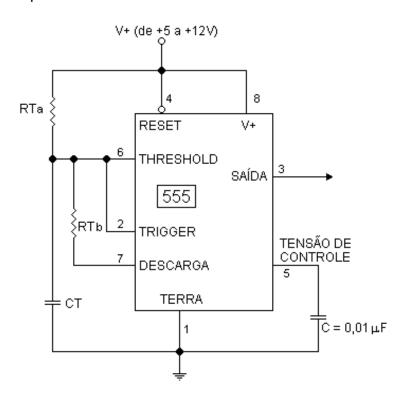

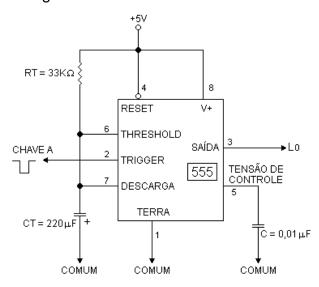

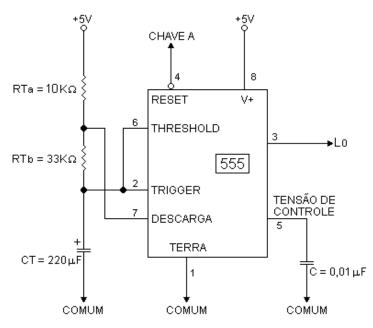

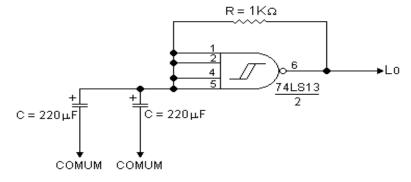

| 13.2.5 O 555                                         | 185 |

| 13.2.6 EXPERIÊNCIA 1                                 | 189 |

| 13.2.7 EXPERIÊNCIA 2                                 | 190 |

| 13.2.8 EXPERIÊNCIA 3                                 | 191 |

| 13.2.9 EXPERIÊNCIA 4                                 | 193 |

| 13.2.10 EXPERIÊNCIA 5                                | 195 |

| 13.2.11 EXPERIÊNCIA 6                                | 195 |

| 13.2.12 EXPERIÊNCIA 7                                | 196 |

| 13.3 EXERCÍCIOS                                      | 198 |

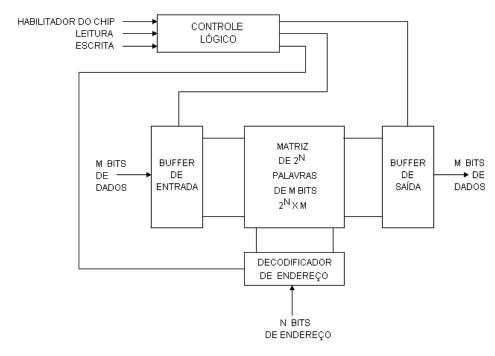

| CAPÍTULO 14 – MEMÓRIAS SEMICONDUTORAS                | 201 |

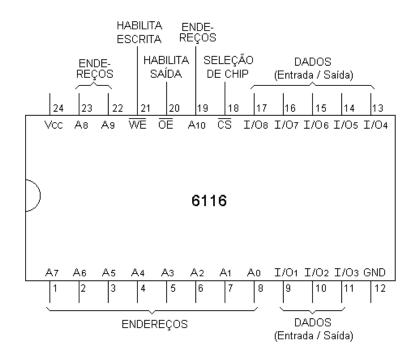

| 14.1 RESUMO                                          | 201 |

| 14.2 MEMÓRIAS RAM's                                  | 201 |

| 14.3 ORGANIZAÇÃO DE UMA MEMÓRIA RAM ESTÁTICA         | 202 |

| 14.4 TEMPOS IMPORTANTES DE MEMÓRIA                   | 203 |

|                                                      |     |

| 14.5 MEMÓRIAS RAM'S BIPOLARES E MOS                                                                                   | 204               |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|

| 14.5.1 EXPERIÊNCIA 1                                                                                                  | 205               |

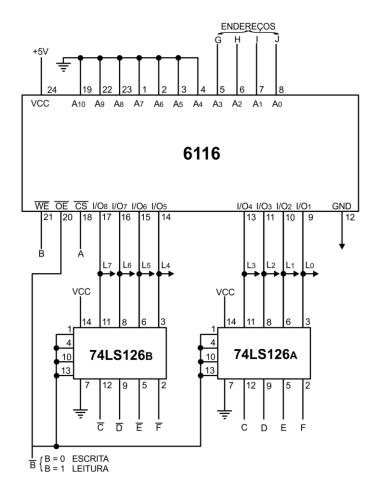

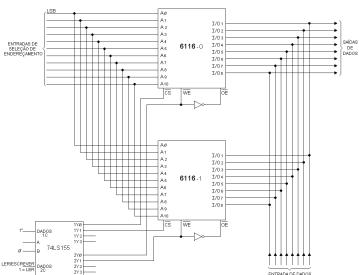

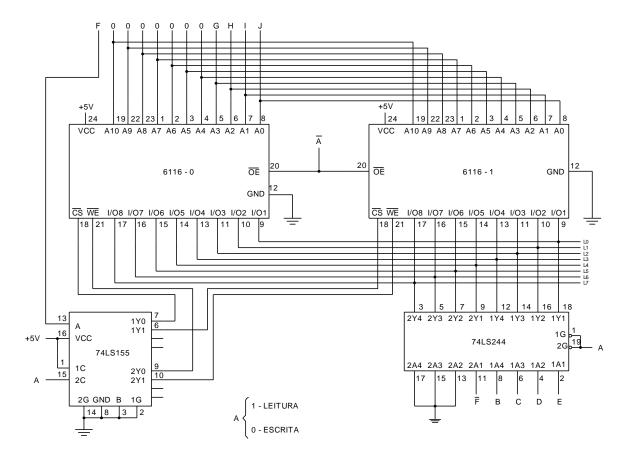

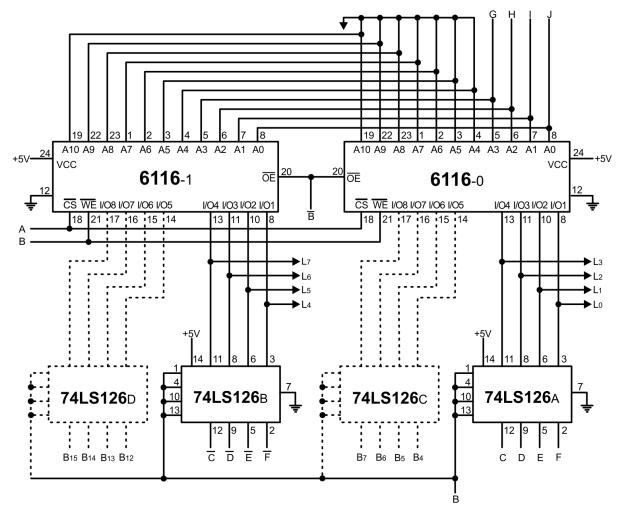

| 14.6 CONSTRUÇÃO DE MEMÓRIAS MAIORES                                                                                   | 208               |

| 14.6.1 EXPERIÊNCIA 2                                                                                                  | 209               |

| 14.6.2 EXPERIÊNCIA 3                                                                                                  | 212               |

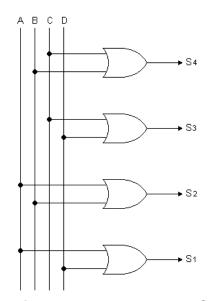

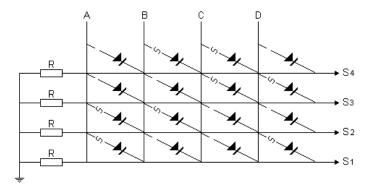

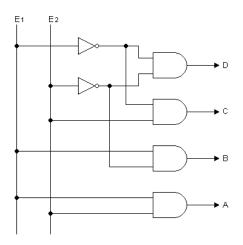

| 14.7 MEMÓRIAS ROM                                                                                                     | 213               |

| 14.7.1 EXPERIÊNCIA 4                                                                                                  | 217               |

|                                                                                                                       |                   |

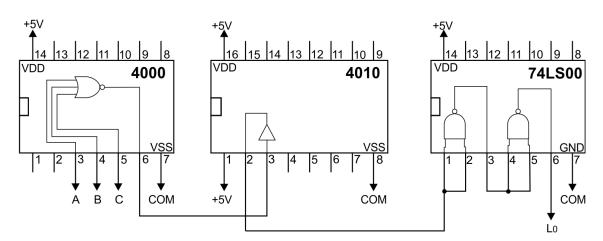

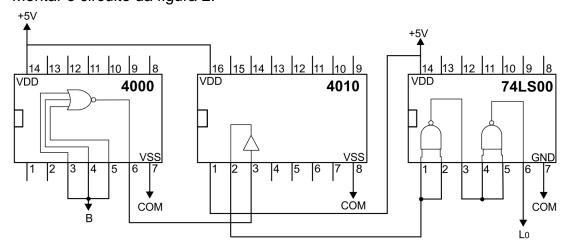

| CAPÍTULO 15 - INTERLIGAÇÕES LÓGICAS OU INTERFACES LÓGICAS                                                             | 219               |

| 15.1 RESUMO                                                                                                           | 219               |

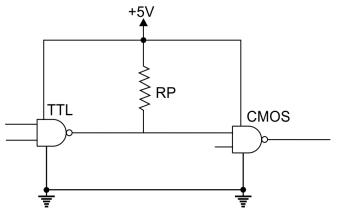

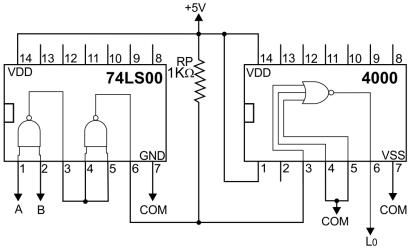

| 15.2 INTERFACES CMOS – TTL                                                                                            | 220               |

|                                                                                                                       |                   |

| 15.2.1 INTERFACES CMOS – TTL DE BAIXA POTÊNCIA (Low-Power)                                                            | 220               |

| <ul> <li>15.2.1 INTERFACES CMOS – TTL DE BAIXA POTÊNCIA (Low-Power)</li> <li>15.2.2 CMOS PARA TTL STANDARD</li> </ul> | 220<br>221        |

| ,                                                                                                                     |                   |

| 15.2.2 CMOS PARA TTL STANDARD                                                                                         | 221               |

| 15.2.2 CMOS PARA TTL STANDARD<br>15.2.2.1 EXPERIÊNCIA 1                                                               | 221<br>221        |

| 15.2.2 CMOS PARA TTL STANDARD 15.2.2.1 EXPERIÊNCIA 1 15.2.2.2 EXPERIÊNCIA 2                                           | 221<br>221<br>222 |

## ATENÇÃO!

O **Módulo Digital Avançado 8810** possue uma **chave de seleção TTL/CMOS**, que quando posicionada em TTL faz com que as chaves de dados, os led's e a ponta de prova operem com **níveis lógicos compatíveis com circuitos TTL's, os quais são alimentados com +5 Volts.**

Estando esta chave posicionada em CMOS, as chaves de dados, os led's e a ponta de prova passam a operar com níveis lógicos compatíveis com circuitos CMOS, que são alimentados com tensão de + 15 Volts.

Deste modo, em todas as experiências deste manual esta chave de seleção deverá permanecer na posição TTL. Em caso contrário, as placas de experiências e o próprio módulo serão danificados.

As condições de garantia do equipamento não cobrem operações indevidas no mesmo.

## CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

## 1.1 FUNÇÃO LÓGICA GATES "E" (AND)

#### **1.1.1 RESUMO**

A função "E" é definida como:

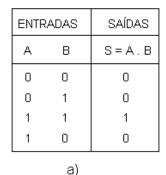

"Produz uma saída 1 somente quando todas as entradas forem 1". Desta maneira o circuito lógico "E" dará um nível alto (1) na saída quando todas as entradas estiverem em nível lógico alto (1). A figura 1 mostra a tabela verdade, o símbolo e a expressão booleana para o gate "E".

Figura 1 - Gate E - a) Tabela Verdade - b) Símbolo - c) Expressão Booleana

#### 1.1.2 OBJETIVO

A familiarização com os GATES E, tabela verdade, conceito de entradas múltiplas e demora de propagação.

#### 1.1.3 EXPERIÊNCIA 1

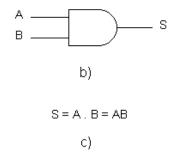

a) Material utilizado: 1 x CI 74LS08

b) Layout do CI 74LS08

Figura 2 - Layout do CI 74LS08

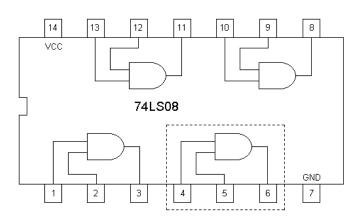

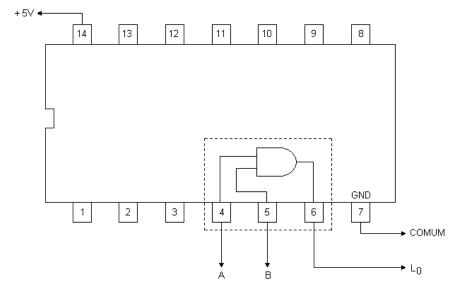

c) Montar a circuito da figura 3.

Figura 3 - Circuito com o GATE E

d) Completar a tabela 1.

| ENTR | ADAS | SAÍDAS     |

|------|------|------------|

| Α    | В    | Lø = A . B |

| Ø    | Ø    |            |

| Ø    | 1    |            |

| 1    | 1    |            |

| 1    | Ø    |            |

**NOTA**: O led aceso indica **1**, apagado **Ø**.

Tabela 1 - Tabela Verdade da Função E de duas entradas.

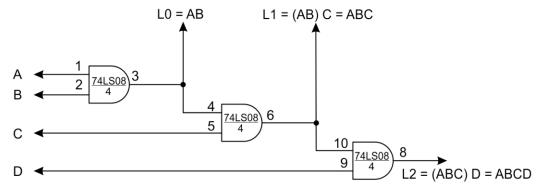

#### 1.1.4 EXPERIÊNCIA 2

- a) Material utilizado: 1 x Cl 74LS08

- b) Montar o circuito da figura 4, ligando o pino 14 ao +15V e o pino 7 ao comum.

Figura 4 - Circuito E de 4 entradas.

c) Completar a tabela 2.

|   | ENTR | RADAS |   |         | SAÍDAS   |           |

|---|------|-------|---|---------|----------|-----------|

| Α | В    | С     | D | L0 = AB | L1 = ABC | L2 = ABCD |

| Ø | Ø    | Ø     | Ø |         |          |           |

| Ø | Ø    | Ø     | 1 |         |          |           |

| Ø | Ø    | 1     | Ø |         |          |           |

| Ø | Ø    | 1     | 1 |         |          |           |

| Ø | 1    | Ø     | Ø |         |          |           |

| Ø | 1    | Ø     | 1 |         |          |           |

| Ø | 1    | 1     | Ø |         |          |           |

| Ø | 1    | 1     | 1 |         |          |           |

| 1 | Ø    | Ø     | Ø |         |          |           |

| 1 | Ø    | Ø     | 1 |         |          |           |

| 1 | Ø    | 1     | Ø |         |          |           |

| 1 | Ø    | 1     | 1 |         |          |           |

| 1 | 1    | Ø     | Ø |         |          |           |

| 1 | 1    | Ø     | 1 |         |          |           |

| 1 | 1    | 1     | Ø |         |          |           |

| 1 | 1    | 1     | 1 |         |          |           |

Tabela 2 - Tabela Verdade do GATE E de 4 entradas.

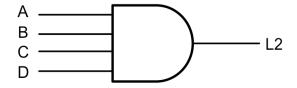

d) Observação: No circuito testado foi montado um gate "E" de 4 entradas usando gates "E" de duas entradas. Usando as propriedades da álgebra de Boole foi feito:

$$L2 = ABCD = (((AB) C) D)$$

Em termos de blocos lógicos, teremos o mostrado na figura 5.

Figura 5 - Gate "E" de 4 entradas.

### 1.1.5 DEMORA DE PROPAGAÇÃO (DELAY TIME)

É o tempo requerido para a saída do gate mudar de estado após as entradas terem mudado.

Um gate TTL típico possui uma demora de propagação de 10ns. Esta demora de propagação depende da tensão de alimentação, temperatura ambiente e da carga capacitiva de saída.

O significado de algumas simbologias referentes a tempo e encontradas nas folhas de dados são:

$\mathbf{t}_{\mathsf{PLH}}$  - Demora de propagação quando a saída está mudando de um nível  $\varnothing$  (baixo), para um nível 1 (alto).

$\mathbf{t}_{\text{PHL}}$  - Demora de propagação quando a saída está mudando de um nível 1 (alto), para um nível  $\varnothing$  (baixo).

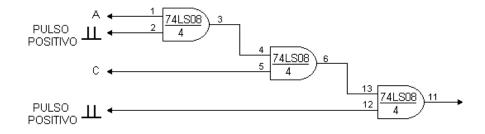

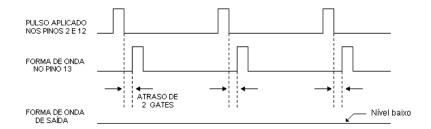

Ambos os parâmetros, **t**<sub>PHL</sub> e **t**<sub>PLH</sub>, são medidas com respeito ao pulso de entrada. Os circuitos das figuras 6 e 8 ilustram a demora de propagação. Devido a estes tempos estarem na ordem de nanosegundos não poderão ser observados a olho nu, e sim com o uso de equipamentos de alta frequência.

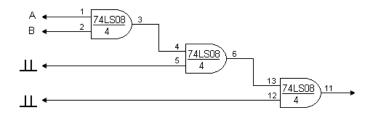

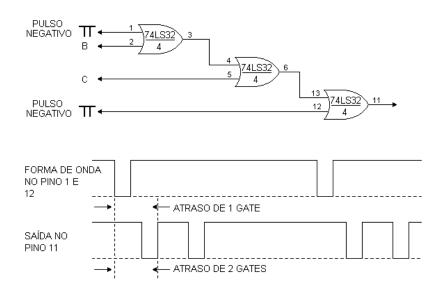

Figura 6 - Circuito para teste de demora de propagação.

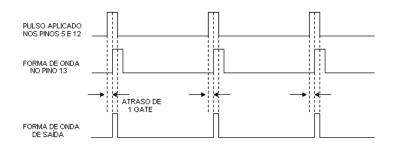

Na figura 6, se A = 1, C = 1 e os pinos 2 e 12 estão ligados a um gerador de pulso ( $\perp \perp$ ) com uma frequência de 1Hz e com largura de pulso menor que a demora de propagação do bloco lógico, então a saída (pino 11) ficaria constantemente em zero, devido aos instantes de ocorrência dos pulsos nos pinos 12 e 13 acontecerem em momentos não coincidentes. A figura 7 ilustra estes atrasos.

Figura 7 - Formas de ondas correspondente a figura 6.

Figura 8 - Circuito para teste de demora de propagação.

Na figura 8, se A = 1 e B = 1, na saída teríamos um pulso a cada segundo, com duração igual ao instante de coincidência dos pulsos. A figura 9 ilustra estes atrasos.

Figura 9 - Formas de onda correspondente a Figura 8

Disto conclui-se que devido à Demora de Propagação de cada *gate* na figura 6, o sinal aplicado no pino 2 vai chegar a entrada do *gate* de saída após ter terminado o pulso introduzido na outra entrada deste *gate*; desta maneira a saída permanece em zero. Na figura 8, o atraso não é suficiente, de maneira que os sinais chegam a tempos próximos um do outro no *gate* de saída, dando assim uma saída adequada, isto, é um pulso.

## CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

## 1.1.6 EXERCÍCIOS

| a)                                             | Em um <i>gate</i> E de 3 entradas A, B e C, para            | $A = 1$ , $B = 1$ e $C = \emptyset$ a saída será: |

|------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|

| <ol> <li>1.</li> <li>2.</li> <li>3.</li> </ol> | 1<br>Ø<br>Indeterminada                                     |                                                   |

| b)                                             | Se ligarmos todas as entradas de um gate E                  | a uma só chave, a saída será:                     |

| <ol> <li>2.</li> <li>3.</li> </ol>             | Igual a entrada<br>O inverso da entrada<br>A função OU      |                                                   |

| c)                                             | A saída de um <i>gate</i> E de 3 entradas pode<br>Booleana: | e ser representada pela expressão                 |

| 1.                                             | (A . B . C )                                                |                                                   |

| 2.                                             | (A . B) C                                                   |                                                   |

| 3.                                             | A (B . C )                                                  |                                                   |

| 4.                                             | (B C) A                                                     |                                                   |

| 5                                              | CAB                                                         |                                                   |

## 1.2 FUNÇÃO LÓGICA GATE "OU" (OR)

#### 1.2.1 **RESUMO**

A função "OU" é definida como:

#### "Se uma ou mais entradas forem 1 a saída será 1".

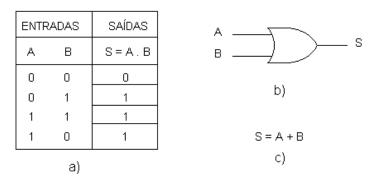

Desta maneira, o circuito lógico "**OU**" dará uma saída alta (1) se pelo menos uma de suas entradas estiver no nível alto (1). A figura 10 mostra a tabela verdade, o símbolo e a expressão booleana para o *gate* "**OU**".

Figura 10 - Gate OU - a) Tabela Verdade - b) Símbolo Lógico - c) Expressão Booleana

#### 1.2.2 OBJETIVO

Neste ponto será examinada a tabela verdade do gate "OU" e o conceito de múltiplas entradas e entradas flutuando.

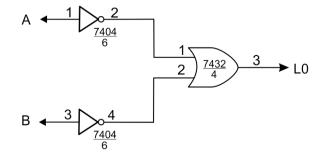

#### 1.2.3 EXPERIÊNCIA 3

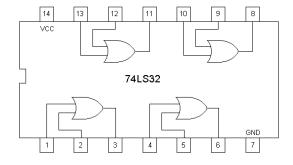

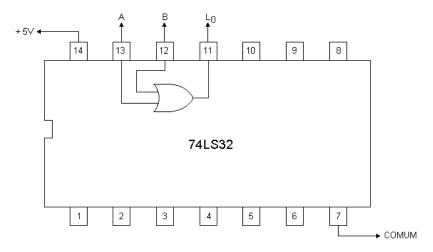

- a) Material utilizado: 1 x CI 74LS32

- b) Layout do CI 74LS32

Figura 11 - Layout do CI 74LS32.

c) Montar o circuito da figura 12.

Figura 12 - Circuito com o Gate OU.

d) Completar a tabela 3.

| ENTR | RADAS | SAÍDAS     |

|------|-------|------------|

| Α    | В     | LØ = A + B |

| Ø    | Ø     |            |

| Ø    | 1     |            |

| 1    | 1     |            |

| 1    | Ø     |            |

Tabela 3 - Tabela Verdade do Gate "OU".

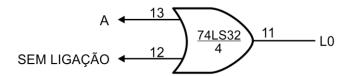

#### 1.2.4 EXPERIÊNCIA 4

a) Material utilizado: 1 x Cl 74LS32

b) Montar o circuito da figura 13

Figura 13 - Gate "OU" com uma entrada flutuando.

#### c) Completar a tabela 4.

| ENTRADAS | SAÍDAS |

|----------|--------|

| Α        | LØ     |

| Ø        |        |

| 1        |        |

Tabela 4 - Tabela Verdade do Gate OU com uma entrada flutuando.

#### Observação:

Notar que o circuito é independente de A, isto significa que o pino 12 (que está flutuando) introduz um nível lógico 1 no circuito.

Isto demonstra uma propriedade dos circuitos integrados da série TTL-74.

"Na tecnologia TTL (série 74) um pino de entrada sem conexão funciona como nível lógico 1".

Na prática, entretanto, para montagens definitivas, não se deve deixar pinos de entradas sem conexão, pois os mesmos poderão operar como antenas recebendo ruídos, que alteram a operação do circuito.

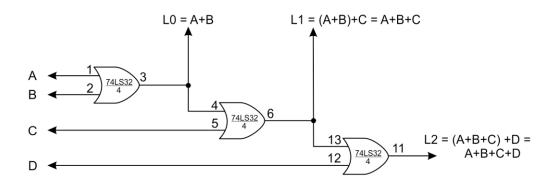

#### 1.2.5 EXPERIÊNCIA 5

- a) Material utilizado: 1 x CI 74LS32

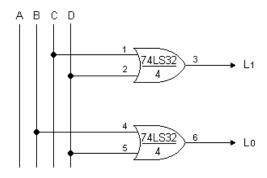

- b) Montar o circuito da figura 14, ligando o pino 14 ao +5V e o pino 7 ao comum.

Figura 14 – Circuito OU de 4 entradas.

### c) Completar a tabela 5.

| ENTRADAS |   |   |   | SAÍDAS   |            |              |

|----------|---|---|---|----------|------------|--------------|

| Α        | В | С | D | L0 = A+B | L1 = A+B+C | L2 = A+B+C+D |

| Ø        | Ø | Ø | Ø |          |            |              |

| Ø        | Ø | Ø | 1 |          |            |              |

| Ø        | Ø | 1 | Ø |          |            |              |

| Ø        | Ø | 1 | 1 |          |            |              |

| Ø        | 1 | Ø | Ø |          |            |              |

| Ø        | 1 | Ø | 1 |          |            |              |

| Ø        | 1 | 1 | Ø |          |            |              |

| Ø        | 1 | 1 | 1 |          |            |              |

| 1        | Ø | Ø | Ø |          |            |              |

| 1        | Ø | Ø | 1 |          |            |              |

| 1        | Ø | 1 | Ø |          |            |              |

| 1        | Ø | 1 | 1 |          |            |              |

| 1        | 1 | Ø | Ø |          |            |              |

| 1        | 1 | Ø | 1 |          |            |              |

| 1        | 1 | 1 | Ø |          |            |              |

| 1        | 1 | 1 | 1 |          |            |              |

Tabela 5 - Tabela Verdade do GATE E de 4 entradas.

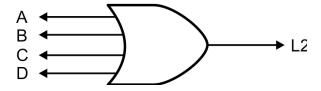

### Observação:

O circuito montado executou a função de um gate "OU" de 4 entradas, porém usa gates "OU" de duas entradas.

Isto foi conseguido lançando mão de uma das propriedades da álgebra de Boole que diz:

$$L2 = A + B + C + D = (((A + B) + C) + D)$$

Em termos de blocos lógicos tem-se o mostrado na figura 15.

Figura 15 - Gates "OU" de 4 entradas.

#### 1.2.6 ANÁLISE DE DEMORA

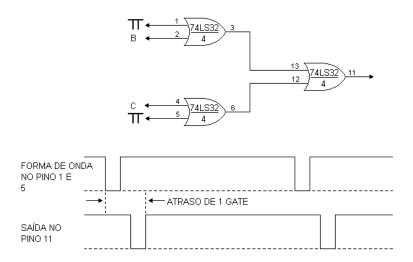

O circuito das figuras 16 e 17 ilustram a demora de propagação.

Figura 16 - Circuito do Gate OU com 4 entradas.

Na figura 16, se B =  $\emptyset$ , C =  $\emptyset$  e os pinos 1 e 12 são ligados a um gerador de pulso negativo ( $\Pi$ ) com uma frequência de 1Hz e com largura de pulso menor que a demora de propagação, ter-se-á na saída, pino 11, a forma de onda apresentada na figura 16. Isto porque o pulso negativo de entrada sofre atrasos diferentes, provocando pulsos adicionais na saída.

Figura 17 - Circuito do Gate "OU" de 4 entradas com demora reduzida.

## CAPÍTULO 1 – GATES LÓGICOS BÁSICOS

Na figura 17, se B =  $\emptyset$ , C =  $\emptyset$  e os pulsos negativos de 1Hz são aplicados aos pinos 1 e 5, a saída, pino 11, apresentaria a forma de onda da figura 17. Isto porque, neste caso, os atrasos seriam de um único bloco lógico e aplicado ao circuito de saída em instantes coincidentes.

Disto conclui-se que apesar dos circuitos das figuras 16 e 17, terem expressões lógicas equivalentes, o circuito da figura 17 introduz menor demora de propagação e, consequentemente, poderá operar em maiores frequências.

#### 1.2.7

| EX | ERCÍC                                | ios                                                                                                                                                                                                         |                                     |                               |

|----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|

| a) |                                      | m bloco " <b>OU</b> " de 4 entradas A, B, C e D, para A =<br>aída será:<br>Alta (1)<br>Baixa (Ø)<br>Indeterminada                                                                                           | = 1, B =<br>(<br>(<br>(             | = Ø, C = Ø e D = ) ) )        |

| b) | para s<br>1.<br>2.<br>3.<br>4.<br>5. | 7                                                                                                                                                                                                           | gates<br>(<br>(<br>(<br>(<br>(<br>( | são necessários ) ) ) ) ) ) ) |

| c) | expres<br>1.<br>2.                   | se disponível um <i>gate "OU</i> " de 5 entradas e<br>ssão L = A+ B. O que deve ser feito com as outras<br>Ligar ao potencial 1<br>Ligar ao potencial Ø1<br>Deixar flutuando1<br>Ligar a uma entrada usada1 |                                     |                               |

| d) | 1.<br>2.                             | aída do gate <b>"OU"</b> é baixa (Ø) isto indica que:<br>Todas as entradas são altas<br>Uma entrada é alta (1)<br>Uma entrada é baixa (Ø)<br>Todas as entradas são baixas (Ø)                               | ( ( (                               | )<br>)<br>)                   |

## 1.3 FUNÇÃO LÓGICA GATE "NÃO" (INVERSOR) (NOT)

#### **1.3.1 RESUMO**

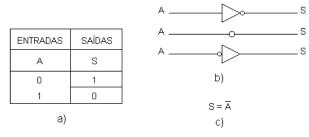

O gate "NÃO" providencia na saída um nível lógico que é o inverso do nível lógico da entrada. A tabela da figura 23a. ilustra esta operação.

Figura 18 - Gate "NÃO" - a) Tabela Verdade - b) Símbolos Lógicos - c) Expressão Booleana.

#### 1.3.2 OBJETIVO

Neste ponto será examinada a tabela verdade do *gate* "NÃO" e algumas aplicações do *gate* "NÃO" como BUFFER e gerador de atraso.

#### 1.3.3 EXPERIÊNCIA 6

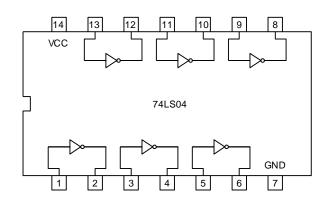

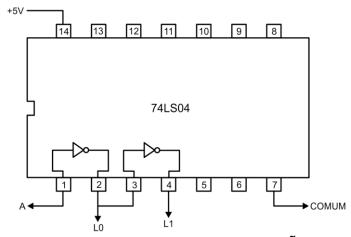

a) Material utilizado: 1 x CI 74LS04

b) Layout do CI 74LS04

Figura 19 - Layout do CI 74LS04.

#### c) Montar o circuito da figura 20.

Figura 20 - Circuito com o gate NÃO.

### d) Completar a tabela 6.

| ENTRADAS | SAÍDAS |                |  |

|----------|--------|----------------|--|

| Α        | LØ = A | <br>LØ = A = a |  |

| Ø        |        |                |  |

| 1        |        |                |  |

Tabela 6 - Tabela Verdade do Gate NÃO (inversor).

### e) Demora de Propagação

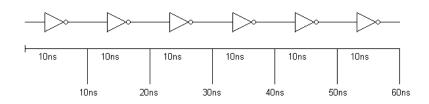

Os gates "NÃO" podem ser usados para introduzir demora de propagação em uma determinada linha. Usados em cascata, como mostra a figura 21, cada gate "NÃO" introduzem um atraso típico de 10ns, para TTL padrão.

Figura 21- Gates NÃO funcionando como Delay (atraso).

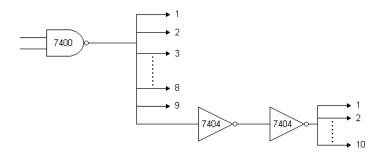

#### f) Fan-Out (Capacidade de Cargas)

Um parâmetro importante dos circuitos integrados é a quantidade de outros gates do mesmo tipo, ou cargas, que a saída de um determinado gate poderá alimentar. Esta característica é chamada "FAN-OUT" e nos circuitos TTL tem valor típico de 10.

Se o circuito exige que mais de 10 cargas devam ser controladas por uma determinada saída, podemos usar gates "NÃO" como BUFFER, de maneira a aumentar este número. A figura 22 ilustra este fato.

Figura 22 - Uso de Gates NÃO como BUFFER.

O circuito original 74LS00 alimenta diretamente apenas 10 entradas, porém neste caso faz o controle de 19, podendo ser expandido para 100.

## CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

## 1.3.4 EXERCÍCIOS

| a) | O gate "NÃO" pode ser usado para inverter dois sinais ao mesmo tempo. |                                         |                 |

|----|-----------------------------------------------------------------------|-----------------------------------------|-----------------|

|    | 1.<br>2.                                                              | Falso<br>Verdadeiro                     |                 |

| b) | Os ga                                                                 | ates "NÃO" podem ser usados como eleme  | ento de demora. |

|    | 1.                                                                    | Falso                                   |                 |

|    | 2.                                                                    | Verdadeiro                              |                 |

|    |                                                                       |                                         |                 |

| c) | Os ga                                                                 | ates "NÃO" podem ser usados como BUFF   | FER.            |

|    | 1.                                                                    | Falso                                   |                 |

|    | 2.                                                                    | Verdadeiro                              |                 |

|    |                                                                       |                                         |                 |

| d) | Um n                                                                  | úmero par de gates "NÃO" ligados em sér | ie:             |

|    | 1.                                                                    | Inverte o sinal de entrada              |                 |

|    | 2.                                                                    | Mantém o mesmo sinal de entrada         |                 |

|    |                                                                       |                                         |                 |

## 1.4 FUNÇÃO LÓGICA GATE "NÃO-E" (NAND)

#### **1.4.1 RESUMO**

A função "NÃO-E" pode ser definida como:

"Produz uma saída Ø somente quando todas as entradas são 1."

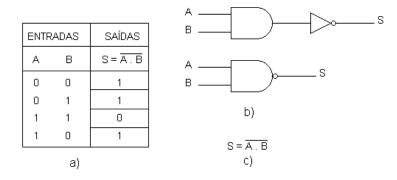

Em suma, o gate "NÃO-E" é o complemento do gate "E". A figura 23 mostra a tabela verdade, o símbolo e a expressão lógica do gate "NÃO-E".

Figura 23 - Gate "NÃO-E" - a) Tabela Verdade - b) Símbolo - c) Expressão Booleana.

#### 1.4.2 OBJETIVO

Será examinada a tabela verdade do gate "NÃO-E", a maneira de montar o circuito NÃO-E com múltiplas entradas e a implementação de qualquer expressão Booleana com apenas o uso de Gates "NÃO-E" (sem a necessidade do uso de outros gates).

#### 1.4.3 EXPERIÊNCIA 7

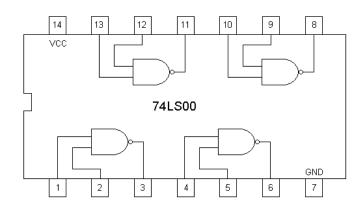

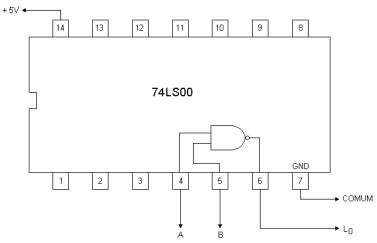

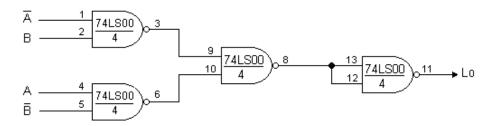

a) Material utilizado: 1 x Cl 74LS00

b) Layout do CI 74LS00

Figura 24 - Lay-out do CI 74LS00.

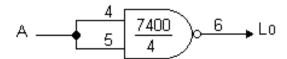

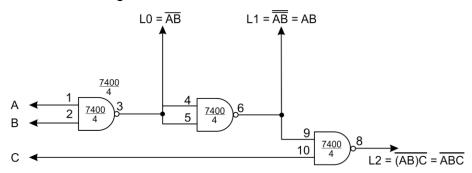

c) A figura 25 mostra o circuito a ser utilizado:

Figura 25 - Circuito com um Gate "NÃO-E".

d) Completar a tabela 7.

| ENTR | RADAS | SAÍDAS  |

|------|-------|---------|

| A B  |       | LØ = AB |

| Ø    | Ø     |         |

| Ø    | 1     |         |

| 1    | 1     |         |

| 1    | Ø     |         |

Tabela 7 - Tabela Verdade do Gate "NÃO-E".

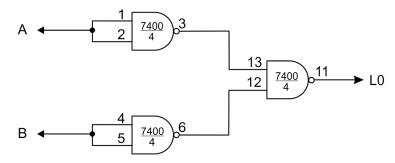

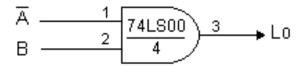

### 1.4.4 EXPERIÊNCIA 8

- a) Material utilizado: 1 x Cl 74LS00

- **b)** Montar o circuito da figura 26, não se esquecendo de ligar o pino 14 ao 5V e o pino 7 ao comum.

Figura 26 - Gate "NÃO-E" funcionando como inversor.

c) Completar a tabela 8.

| ENTRADAS | SAÍDAS |

|----------|--------|

| Α        | LØ = Ā |

| Ø        |        |

| 1        |        |

Tabela 8 - Tabela Verdade do gate "NÃO-E" funcionando como inversor.

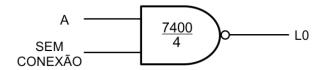

d) Montar o circuito da figura 27

Figura 27 – Gate NÃO-E funcionando como inversor.

e) Completar a tabela 9

| ENTRADAS | SAÍDAS |

|----------|--------|

| Α        | LØ = Ā |

| Ø        |        |

| 1        |        |

Tabela 9 – Tabela Verdade do gate NÃO-E funcionando como inversor.

### **CONCLUSÃO:**

O gate "NÃO-E" quando tem as entradas ligadas no mesmo ponto, ou quando é usada apenas uma das entradas deixando as outras flutuando funciona como um gate "NÃO". No primeiro caso a entrada do circuito equivalente a 1 unidade de carga, quando em nível lógico baixo e 2 unidades de carga, quando em nível lógico alto.

No segundo caso, será sempre uma unidade de carga, porém, para altas frequências o pino aberto poderá operar com uma antena, fornecendo ruídos para o circuito. Neste caso é melhor que o pino seja conectado a nível lógico alto, ao invés de deixá-lo aberto.

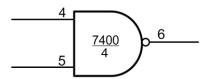

#### 1.4.5 EXPERIÊNCIA 9

a) Material utilizado: 1 x CI 74LS00

**b)** Montar o circuito da figura 28.

Figura 28 – Circuito do Gate NÃO-E de 3 entradas.

#### c) Completar a tabela 10

| EN | TRAD | AS | SAÍDAS  |         |          |

|----|------|----|---------|---------|----------|

| Α  | В    | C  | L0 = AB | L1 = AB | L2 = ABC |

| Ø  | Ø    | Ø  |         |         |          |

| Ø  | Ø    | 1  |         |         |          |

| Ø  | 1    | Ø  |         |         |          |

| Ø  | 1    | 1  |         |         |          |

| 1  | Ø    | Ø  |         |         |          |

| 1  | Ø    | 1  |         |         |          |

| 1  | 1    | Ø  |         |         |          |

| 1  | 1    | 1  |         |         |          |

Tabela 10 - Tabela Verdade do gate "NÃO E" de 4 entradas.

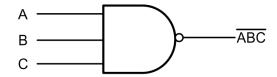

## **CONCLUSÃO:**

O circuito montado na figura 28 pode ser representado simbolicamente como mostra a figura 29.

Figura 29 - Gate "NÃO-E" de 3 entradas (símbolo).

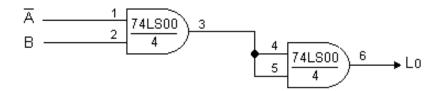

#### 1.4.6 EXPERIÊNCIA 10

- c) Material utilizado: 1 x Cl 74LS00

- d) Montar o circuito da figura 30.

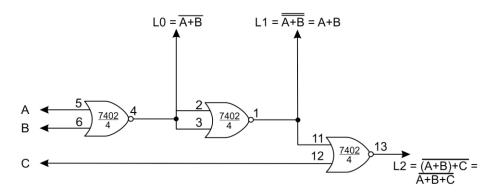

Figura 30 – Circuito do gate "OU" montado com gates "NÂO-E".

## c) Completar a tabela 11

| ENTR | ADAS | SAÍDAS                                                 |

|------|------|--------------------------------------------------------|

| Α    | В    | $LØ = \overline{\overline{A}} \overline{\overline{B}}$ |

| Ø    | Ø    |                                                        |

| Ø    | 1    |                                                        |

| 1    | 1    |                                                        |

| 1    | Ø    |                                                        |

Tabela 11 – Tabela Verdade do circuito do gate "OU" montado com gates "NÃO-E".

## **CONCLUSÃO:**

Comparar o resultado da tabela 11 com a tabela do gate "OU" e notar que são idênticas. Isto pode ser explicado através do teorema da álgebra de Boole chamado **Teorema de De Morgan.**

$$\overline{\overline{A}} \overline{\overline{B}} = A + B$$

Deste modo, se observa que podendo-se implementar o gate "OU" com Gates "NÂO-E", qualquer expressão Booleana pode ser montado usando apenas Gates "NÂO-E".

#### 1.4.7 EXPERIÊNCIA 11

- a) Material utilizado: 1 x CI 74LS00, ponta de prova do equipamento (PP)

- b) Montar o circuito da figura 31.

Figura 31 – Circuito para teste de Nível Lógico de Entrada.

c) Completar a tabela 12, colocando a ponta de prova (PP) nos pinos assinalados e anotando a indicação lógica do display.

| PONTA DE PROVA | INDICAÇÃO LÓGICA |

|----------------|------------------|

| Pino 4         |                  |

| Pino 5         |                  |

| Pino 6         |                  |

Tabela 12 – Teste de Níveis Lógicos de um gate "NÂO-E".

# **CONCLUSÃO:**

Observar que nas entradas desconectada a ponta de prova (PP) indicou nível lógico falso, isto é a tensão deve estar entre 0,7V e 2,1V. Porém na saída à ponta de prova indicou nível lógico "0". Disto conclui-se que as entradas abertas foram interpretadas pelo gate como nível "1".

A série 74 foi construída de maneira que as entradas desconectadas sejam entendidas como nível lógico "1", embora a tensão nelas se apresente em torno de 1,4V, que é um nível lógico falso, ou seja, está na região de transição lógica.

### MÓDULO 8810 – MANUAL TEÓRICO E PRÁTICO

# **CAPÍTULO 1 – GATES LÓGICOS BÁSICOS**

## 1.4.8 EXERCÍCIOS

| a) | Em um gate "NÃO-E" de 3 entradas, duas entradas são conectadas ao +5 a terceira é ligada a chave A, a saída será: |                                   |                             |  |

|----|-------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|--|

|    | 1.                                                                                                                | A                                 |                             |  |

|    | 2.                                                                                                                | Ā                                 |                             |  |

|    | 3.                                                                                                                | 1                                 |                             |  |

|    | 4.                                                                                                                | Ø                                 |                             |  |

| b) | Com                                                                                                               | gates "NÃO-E" pode-se executar qu | ualquer expressão Booleana. |  |

|    | 1.                                                                                                                | Certo                             |                             |  |

|    | 2.                                                                                                                | Errado                            |                             |  |

|    |                                                                                                                   |                                   |                             |  |

# 1.5 FUNÇÃO LÓGICA GATE "NÃO-OU" (NOR)

#### **1.5.1 RESUMO**

A função "NÃO-E" pode ser definida como:

#### "Produz uma saída Ø se uma ou mais entradas forem 1."

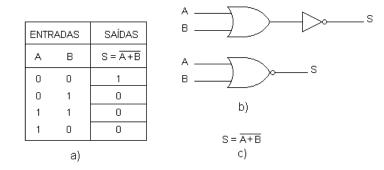

Isto que dizer que o gate "NÂO-OU" é complemento do gate "OU". A figura 32 mostra a tabela verdade, o símbolo e a expressão Booleana do gate "NÂO-OU".

Figura 32 - Gate "NÃO-OU" - a) Tabela Verdade - b) Símbolo Lógico - c) Expressão Booleana.

#### 1.5.2 OBJETIVO

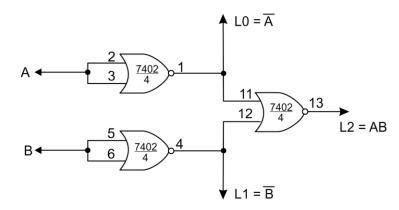

Será examinada a tabela verdade do gate "NÃO-OU", seu uso como inversor e implementação de gates "NÃO-OU" com múltiplas entradas, execução de qualquer expressão Booleana usando Gates "NÂO-OU", ponto "E" (lógica por fios).

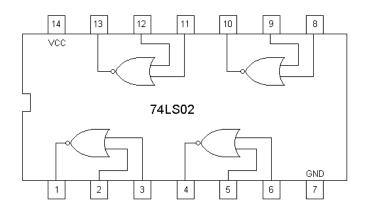

#### 1.5.3 EXPERIÊNCIA 12

a) Material utilizado: 1 x CI 74LS02

**b)** Layout do CI 74LS02

Figura 33 - Layout do CI 74LS02.

c) Montar o circuito da figura 34, não se esquecendo de ligar 14 ao +5V e o pino 7 ao comum.

Figura 34 - Circuito com o gate "NÃO-OU".

d) Completar a tabela 13.

| ENTR | RADAS | SAÍDAS   |

|------|-------|----------|

| Α    | В     | LØ = A+B |

| Ø    | Ø     |          |

| Ø    | 1     |          |

| 1    | 1     |          |

| 1    | Ø     |          |

Figura 13 - Tabela Verdade do gate NÃO-OU.

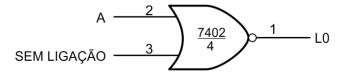

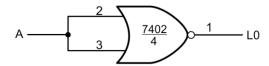

## 1.5.4 EXPERIÊNCIA 13

- a) Material utilizado: 1 x Cl 74LS02

- **b)** Montar o circuito da figura 35.

Figura 35 - Circuito com o gate "NÃO-OU".

c) Completar a tabela 14.

| ENTRADAS | SAÍDAS |

|----------|--------|

| A        | LØ     |

| Ø        |        |

| 1        |        |

Tabela 14 - Tabela Verdade do gate "OU" com uma entrada flutuando.

# **CONCLUSÃO:**

Da tabela da figura 14, nota-se que o circuito não executa função lógica (L0 sempre  $\emptyset$ ). Isto é devido ao pino 3 estar flutuando, o que equivale a introdução de um nível "1" no gate, produzindo assim sempre uma saída " $\emptyset$ ".

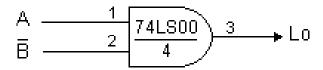

#### 1.5.5 EXPERIÊNCIA 14

- a) Material utilizado: 1 x Cl 74LS02

- **b)** Montar o circuito da figura 36.

Figura 36 - Circuito com o gate "NÃO-OU" funcionando como Inversor.

c) Completar a tabela 15.

| ENTRADAS | SAÍDAS |

|----------|--------|

|          |        |

| Α        | LØ     |

| Ø        |        |

| 1        |        |

Tabela 15 - Tabela Verdade do gate "OU" com uma entrada ligada ao comum.

d) Montar o circuito da figura 37.

Figura 37 – Circuito com gate "NÃO-OU" funcionando como inversor.

e) Completar a tabela 16.

| ENTRADAS | SAÍDAS |

|----------|--------|

|          |        |

| Α        | LØ     |

| Ø        |        |

| 1        |        |

Tabela 16 - Tabela Verdade do gate "NÃO-OU" com uma entrada ligada ao mesmo ponto.

# **CONCLUSÃO:**

Nos dois circuitos apresentados o gate "NÃO-OU está funcionando como inversor.

### 1.5.6 EXPERIÊNCIA 15

- a) Material utilizado: 1 x CI 74LS02

- **b)** Montar o circuito da figura 38.

Figura 38 - Gate "NÃO-OU" de 3 entradas.

# c) Completar a tabela 17

| EN | ENTRADAS |   | SAÍDAS   |          |            |

|----|----------|---|----------|----------|------------|

| Α  | В        | С | L0 = A+B | L1 = A+B | L2 = A+B+C |

| Ø  | Ø        | Ø |          |          |            |

| Ø  | Ø        | 1 |          |          |            |

| Ø  | 1        | Ø |          |          |            |

| Ø  | 1        | 1 |          |          |            |

| 1  | Ø        | Ø |          |          |            |

| 1  | Ø        | 1 |          |          |            |

| 1  | 1        | Ø |          |          |            |

| 1  | 1        | 1 |          |          |            |

Tabela 17 - Tabela Verdade do gate "NÃO OU" de 3 entradas.

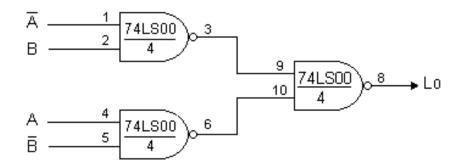

### 1.5.7 EXPERIÊNCIA 16

- a) Material utilizado: 1 x Cl 74LS02.

- **b)** Montar o circuito da figura 39.

Figura 39 – Gate "E" implementado com Gates "NÃO OU".

### c) Completar a tabela 18.

| ENTR | ADAS |        | SAÍDAS |         |

|------|------|--------|--------|---------|

| Α    | В    | L0 = A | L1 = B | L2 = AB |

| Ø    | Ø    |        |        |         |

| Ø    | 1    |        |        |         |

| 1    | Ø    |        |        |         |

| 1    | 1    |        |        |         |

Figura 18 - Tabela Verdade do circuito da figura 39.

### **CONCLUSÃO:**

O circuito apresentado representa a função "E", deste modo podemos deduzir que com o gate "NÃO-OU" é possível montar qualquer expressão Booleana.

O processo de se conseguir isto é através do Teorema de De Morgan:

$$\overline{\overline{A} + \overline{B}} = A \cdot B$$

### 1.5.8 EXPERIÊNCIA 17

a) Material utilizado: 1 x Cl 74LS02.

**b)** Montar o circuito da figura 40.

Figura 40 – Circuito que executa lógica por fios.

## Observação:

Não é possível visualizar somente A+B e nem C+D sem que se desfaça o ponto E.

c) Completar teoricamente a tabela 19 e comparar com o resultado prático.

| ENTRADAS |   |   | SAÍDAS |                                          |

|----------|---|---|--------|------------------------------------------|

| Α        | В | С | D      | $L0 = \overline{(A+B)} (\overline{C+D})$ |

| 1        | 1 | 1 | 1      |                                          |

| Ø        | Ø | 1 | 1      |                                          |

| Ø        | Ø | Ø | Ø      |                                          |

| 1        | 1 | Ø | Ø      |                                          |

Figura 19 - Tabela Verdade do circuito com lógica por fios.

Como os led's L<sub>0</sub>, L<sub>1</sub> e L<sub>2</sub> estão conectador ao mesmo ponto, prevalece a lógica "E" por fios, ou seja, o valor de L<sub>2</sub>.

#### CONCLUSÃO:

A lógica por fios, ou ponto "E", é uma condição onde as saídas de dois ou mais Gates são ligadas juntas.

Neste circuito, as saídas de todos os Gates devem ter nível "1" para produzir uma saída "1" no ponto "E". Se uma das saídas dos Gates for "0" esta saída manterá o ponto "E" um nível "0", independente do valor de outra saída.

O circuito montado, usando lógica por fios, economiza um gate "E", porém esta configuração não é recomendada por circuitos TTL standard, devido ao grande consumo de corrente. Algumas famílias lógicas podem produzir o ponto, porém TTL produz o ponto "E", e pode ser ligadas no máximo duas saídas de gates no mesmo ponto.

## MÓDULO 8810 – MANUAL TEÓRICO E PRÁTICO

# CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

# 1.5.9 EXERCÍCIOS

| a) |       | ma entrada de um gate " <b>NÃO-OU</b> " é 1 e a<br>ndo ser 1 ou Ø, qual será a saída:       | s outras são desconhecidas, |

|----|-------|---------------------------------------------------------------------------------------------|-----------------------------|

|    | 1.    | 1                                                                                           |                             |

|    | 2.    | Ø                                                                                           |                             |

|    | 3.    | Indeterminada                                                                               |                             |

| b) |       | implementar a função S = A + B + C + D, entradas e sem o uso da lógica por fios, <i>qua</i> |                             |

|    | 1.    | 2                                                                                           |                             |

|    | 2.    | 4                                                                                           |                             |

|    | 3.    | 6                                                                                           |                             |

|    | 4.    | 8                                                                                           |                             |

|    |       |                                                                                             |                             |

| c) | A Lóg | jica por fios                                                                               |                             |

|    | 1.    | É uma boa prática em TTL                                                                    |                             |

|    | 2.    | Reduz o número de gates necessários                                                         |                             |

|    | 3.    | Pode ser usadas com várias saída de gates                                                   | ligadas juntas              |

| d) | Com   | gates " <b>NÃO-OU</b> " pode-se executar qualque                                            | er expressão Booleana.      |

|    | 1.    | Errado                                                                                      |                             |

|    | 2.    | Certo                                                                                       |                             |

|    |       |                                                                                             |                             |

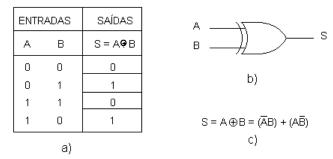

# 1.6 FUNÇÃO LÓGICA GATE "OU-EXCLUSIVO" (XOR)

#### **1.6.1 RESUMO**

O gate "OU-EXCLUSIVO" e um gate "OU" modificado, no qual uma entrada "1" produz uma saída "1", porém se mais de uma entrada for "1" a saída será "0", e também se todas as entradas forem "0" a saída será "0". Deste modo podemos definir a função "OU-EXCLUSIVO" como:

#### "Produz uma saída "1" somente se as entradas forem diferentes."

A figura 60 apresenta uma tabela verdade, símbolo e expressão Booleana do gate OU-EXCLUSIVO.

Figura 41 - Gate "OU-EXCLUSIVO" a) Tabela Verdade - b) Símbolo - c) Expressão Booleana

#### 1.6.2 OBJETIVO

Será examinada a implementação da função "OU-EXCLUSIVO" com Gates "E", "OU", "NÃO-E", "NÃO-OU" e com Gates "OU-EXCLUSIVO" disponível em CI.

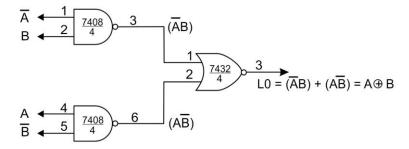

### 1.6.3 EXPERIÊNCIA 18

- a) Material utilizado: 1 x Cl 74LS08 e 1 x Cl 74LS32.

- **b)** Montar o circuito da figura 42, não se esquecendo de alimentar os Cl's (+5V e comum).

Figura 42 - Gate para gerar a função "OU-EXCLUSIVO".

c) Completar as tabela 20.

| ENTRADAS |   | SAÍDAS     |

|----------|---|------------|

| Α        | В | LØ = A ⊕ B |

| Ø        | Ø |            |

| Ø        | 1 |            |

| 1        | 1 |            |

| 1        | Ø |            |

Tabela 20 - Tabela Verdade da função "OU-EXCLUSIVO".

# **CONCLUSÃO:**

Notar que a função "OU-EXCLUSIVO" é montada a partir da expressão Booleana.

$$A \oplus B = \overline{AB} + A\overline{B}$$

Usando assim dois Gates "E" e um gate "OU"

#### 1.6.4 EXPERIÊNCIA 19

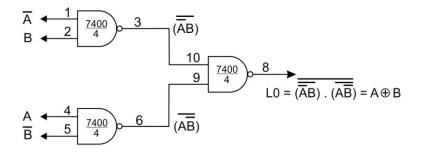

- a) Material utilizado: 1 x CI 74LS00

- **b)** Montar o circuito da figura 43, não se esquecendo de alimentar os CI (+5V e comum).

Figura 43 – Função "OU-EXCLUSIVO" montada com gates "NÃO-E".

c) Completar as tabelas 21.

| ENTR | ADAS | SAÍDAS     |

|------|------|------------|

| Α    | В    | LØ = A ⊕ B |

| Ø    | Ø    |            |

| Ø    | 1    |            |

| 1    | 1    |            |

| 1    | Ø    |            |

Tabela 21 - Tabela Verdade da função "OU-EXCLUSIVO", montada com gates "NÃO-E".

## **CONCLUSÃO:**

A função "OU-EXCLUSIVO" implementando com Gates "NÃO-E" é conseguida com o uso do teorema de De Morgan como se segue:

$$A \oplus B = \overline{AB} + A\overline{B} = \overline{\overline{AB}} = \overline{\overline{AB}} = \overline{\overline{AB}}$$

Comparando os resultados das tabelas Verdades vemos a validade da aplicação do teorema.

### 1.6.5 EXPERIÊNCIA 20

- a) Material utilizado: 1 x Cl 74LS02

- b) Montar o circuito da figura 44.

Figura 44 – Função "OU-EXCLUSIVO", montada com gates "NÃO-OU".

c) Completar as tabelas 22.

| ENTR | ADAS | SAÍDAS     |

|------|------|------------|

| Α    | В    | LØ = A ⊕ B |

| Ø    | Ø    |            |

| Ø    | 1    |            |

| 1    | 1    |            |

| 1    | Ø    |            |

Tabela 22 - Tabela Verdade da função "OU-EXCLUSIVO", montada com gates "NÃO-OU".

### **CONCLUSÃO:**

A função "OU-EXCLUSIVO" montada com gates 'NÃO-OU', é conseguida com a aplicação do teorema de De Morgan, cujos resultados podem ser conferidos comparando as tabelas verdades.

$$A \oplus B = \overline{A}B + A\overline{B} = (\overline{\overline{A}B}) + (\overline{A}\overline{\overline{B}}) = (\overline{\overline{A}+\overline{B}}) + (\overline{\overline{A}+\overline{B}})$$

$$A \oplus B = (\overline{\overline{A}+\overline{B}}) + (\overline{\overline{\overline{A}+B}})$$

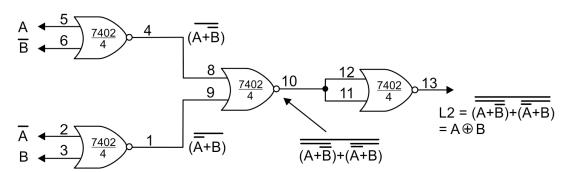

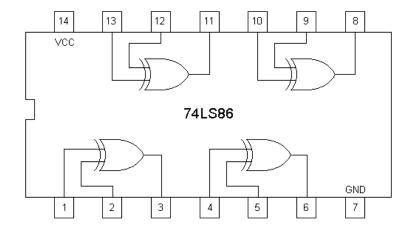

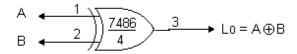

#### 1.6.6 EXPERIÊNCIA 21

- a) Material utilizado: 1 x Cl 74LS86

- b) Layout do CI 74LS86.

Figura 45 - Lay-out do CI 74LS86.

c) Mostrar o circuito da figura 46.

d) Completar as tabelas 23 e 24.

| ENTRADAS |   | SAÍDAS     |

|----------|---|------------|

| Α        | В | LØ = A ⊕ B |

| Ø        | Ø |            |

| Ø        | 1 |            |

| 1        | 1 |            |

| 1        | Ø |            |

Tabela 23 - Tabela Verdade do gate "OU-EXCLUSIVO".

| ENTRADAS |   | SAÍDAS |

|----------|---|--------|

| Α        | В | LØ     |

| Ø        | Ø |        |

| 1        | Ø |        |

| Ø        | 1 |        |

| 1        | 1 |        |

Tabela 24 - Tabela Verdade do gate "OU-EXCLUSIVO" funcionando como um Inversor Programável.

e) Observar na tabela 24 que quando B = Ø, a saída do gate "OU-EXCLUSIVO" apresenta o nível lógico idêntico ao da entrada A. Porém, quando B = 1 a saída é o inverso de "A". Deste modo, o gate "OU-EXCLUSIVO" pode ser usado como um inversor programável; se uma das entradas é Ø não há inversão, porém se for 1 há inversão do nível lógico da outra entrada.

## MÓDULO 8810 – MANUAL TEÓRICO E PRÁTICO

# CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

# 1.6.7 EXERCÍCIOS

| a) | O gate "OU-EXCLUSIVO" produz uma saída 1 se: |                                                    |                   |  |  |  |  |

|----|----------------------------------------------|----------------------------------------------------|-------------------|--|--|--|--|

|    | 1.                                           | Ambas as entradas forem Ø                          |                   |  |  |  |  |

|    | 2.                                           | As entradas forem estados contrários               |                   |  |  |  |  |

|    | 3.                                           | Ambas as entradas forem 1                          |                   |  |  |  |  |

|    | 4.                                           | Nenhuma das respostas anteriores                   |                   |  |  |  |  |

|    |                                              |                                                    |                   |  |  |  |  |

| b) |                                              | gate "OU-EXCLUSIVO" produz uma saída Ø se as smas. | entradas forem as |  |  |  |  |

|    | 1.                                           | Verdade                                            |                   |  |  |  |  |

|    | 2.                                           | Falso                                              |                   |  |  |  |  |

|    |                                              |                                                    |                   |  |  |  |  |

| c) | Par                                          | ra usar o gate "OU-EXCLUSIVO" como inversor:       |                   |  |  |  |  |

|    | 1.                                           | As entradas devem ser 1 simultaneamente            |                   |  |  |  |  |

|    | 2.                                           | As entradas devem ser Ø simultaneamente            |                   |  |  |  |  |

|    | 3.                                           | Uma entrada deve ser sempre Ø                      |                   |  |  |  |  |

|    | 4.                                           | Uma entrada deve ser sempre 1                      |                   |  |  |  |  |

# 1.7 TEOREMA DE "DE MORGAN"

#### **1.7.1 RESUMO**

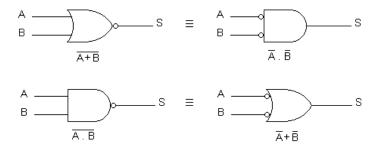

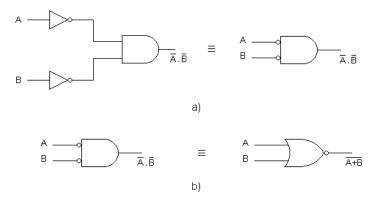

Basicamente, o teorema de De Morgan permite a execução de uma expressão Booleana usando determinados tipos de gates, por exemplo "NÃO-E" ou então "NÃO-OU". O teorema funciona da seguinte maneira:

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

$\overline{A \cdot B} = \overline{A} + \overline{B}$

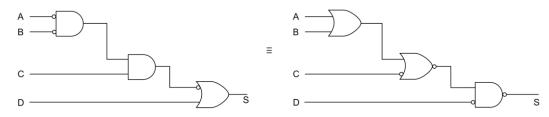

Isto está mostrado em símbolos na figura 47.

Figura 47 - Teorema De Morgan.

Deste modo podemos passar de um tipo de função a outra pela aplicação do Teorema de De Morgan.

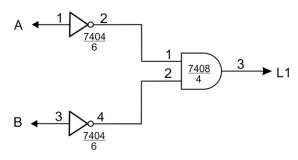

### 1.7.2 EXPERIÊNCIA 22

- a) Material utilizado: 1 x CI 74LS04 e 1 x CI 74LS32.

- **b)** Montar o circuito da figura 48, não se esquecendo de alimentar os Cl's (+5V e comum).

Figura 48 – Implementação do Teorema de De Morgan.

### c) Completar a tabela 25.

| ENTR | ADAS | SAÍDAS   |

|------|------|----------|

| Α    | В    | LØ = A+B |

| Ø    | Ø    |          |

| Ø    | 1    |          |

| 1    | 1    |          |

| 1    | Ø    |          |

Tabela 25 - Tabela Verdade da expressão  $\overline{A} + \overline{B}$

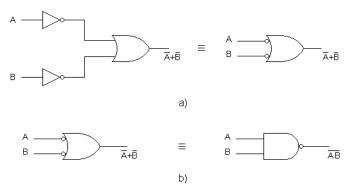

### **CONCLUSÃO:**

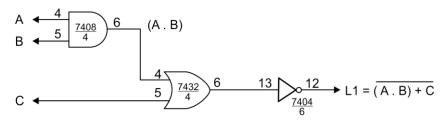

O circuito montado representa a função NÂO-E, e pode ser provado comparando o resultado da tabela verdade com a já visto no gate "NÃO-E". Deste modo, observamos que a troca da função "OU" para "E", foi acompanhada de inversão do sinal nas barras de entrada e saída, como mostra a figura 49 em símbolos lógicos.

Figura 49 - a) Representação Simbólica do circuito montado - b) Identidade pelo Teorema de De Morgan.

#### 1.7.3 EXPERIÊNCIA 23

- a) Material utilizado: 1 x CI 74LS04 e 1 x CI 74LS08.

- b) Montar o circuito da figura 50, não se esquecendo de alimentar os Cl's (+5V e comum).

Figura 50 – Implementação do teorema de De Morgan.

c) Completar a tabela 26.

| ENTR | RADAS | SAÍDAS     |

|------|-------|------------|

| Α    | В     | LØ = A . B |

| Ø    | Ø     |            |

| Ø    | 1     |            |

| 1    | 1     |            |

| 1    | Ø     |            |

Tabela 26 - Tabela Verdade da expressão A. B.

# **CONCLUSÃO:**

O circuito montado representa a função "NÂO-OU", o que pode ser comprovado pelas tabelas verdades. Observamos que a troca de função "E" para "OU" foi acompanhada de uma inversão nos sinais de entrada e saída, como podemos ver em símbolos na figura 51.

Figura 51 - a) Representação Simbólica do circuito montado - b) Identidade pelo Teorema De Morgan.

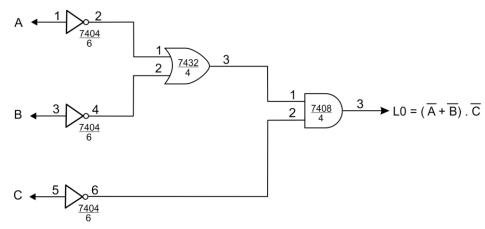

### 1.7.4 EXPERIÊNCIA 24

- a) Material utilizado: 1 x Cl 74LS04, 1 x Cl 74LS08 e Cl 74LS32.

- **b)** Montar o circuito da figura 52, não se esquecendo de alimentar os Cl's (+5V e comum).

Figura 52 – Circuito da expressão Booleana ( $\overline{A} + \overline{B}$ ).  $\overline{C}$

c) Completar a tabela 27.

| ENTRADAS |   | AS | SAÍDAS                                                  |

|----------|---|----|---------------------------------------------------------|

| Α        | В | С  | $L0 = (\overline{A} + \overline{B}) \cdot \overline{C}$ |

| Ø        | Ø | Ø  |                                                         |

| Ø        | Ø | 1  |                                                         |

| Ø        | 1 | Ø  |                                                         |

| Ø        | 1 | 1  |                                                         |

| 1        | Ø | Ø  |                                                         |

| 1        | Ø | 1  |                                                         |

| 1        | 1 | Ø  |                                                         |

| 1        | 1 | 1  |                                                         |

Tabela 27 - Tabela Verdade da expressão ( $\overline{A} + \overline{B}$ ).  $\overline{C}$ .

d) Sem desmontar o circuito anterior, montar o circuito da figura 53.

Figura 53 – circuito da expressão (A.B) + C

e) Completar a tabela 28.

| ENTRADAS |   | AS | SAÍDAS           |

|----------|---|----|------------------|

| Α        | В | С  | L1 = (A . B) + C |

| Ø        | Ø | Ø  |                  |

| Ø        | Ø | 1  |                  |

| Ø        | 1 | Ø  |                  |

| Ø        | 1 | 1  |                  |

| 1        | Ø | Ø  |                  |

| 1        | Ø | 1  |                  |

| 1        | 1 | Ø  |                  |

| 1        | 1 | 1  |                  |

Tabela 28 - Tabela Verdade da expressão ( A . B) + C

#### **CONCLUSÃO:**

Observar que os resultados das tabelas verdades 27 e 28 são idênticos. Isto nos mostra a aplicação do teorema de **De Morgan** de maneira mais ampla. O realizado nesta experiência, em termos de expressão Booleana, foi:

$$(\overline{A} + \overline{B}) \cdot \overline{C} = (\overline{\overline{A} + \overline{B}}) \cdot \overline{\overline{C}} = (\overline{\overline{A} + \overline{B}}) + \overline{\overline{C}} =$$

$$= (\overline{\overline{A}} \cdot \overline{\overline{B}}) + C = (\overline{A} \cdot \overline{B}) + C$$

Logo,  $(\overline{A} + \overline{B}) \cdot \overline{C} = (\overline{A} \cdot \overline{B}) + C$

Em termos de símbolos temos a figura 54.

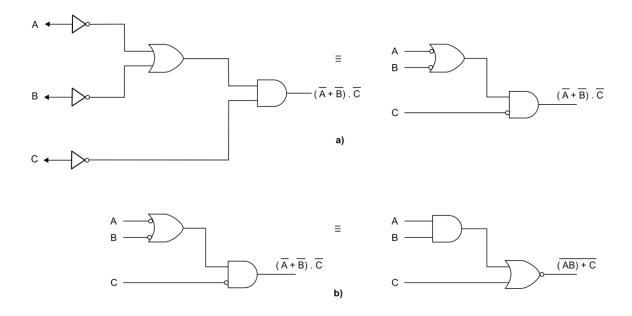

Figura 54 - a) Representação simbólica do circuito da figura 78 – b) Identidade pelo Teorema de De Morgan.

Analisando a representação simbólica dos circuitos, podem-se enunciar algumas regras práticas para que, dispondo de um circuito, se possa fazer aplicação do teorema de De Morgan sem a necessidade de recorrer a expressão Booleana:

"Dispondo de um circuito, a aplicação do teorema de De Morgan se faz trocandose todas as funções "E" por "OU" e "OU" por "E", e fazendo a inversão de todas as entradas e saídas, de modo que duas inversões na mesma linha se anulam."

## 1.7.5 EXERCÍCIOS

- a) A função "E" pode ser implementado com gates:

- 1. E

- 2. OU

- 3. NÃO-E

- 4. NÃO-OU

- 5. Nenhum dos itens anteriores

- b) Pelo teorema de De Morgan a expressão  $S = \overline{A + B}$  é semelhante a:

- 1.  $\overline{A} \cdot \overline{B}$

- 2. A.B

- 3.  $\overline{A} + \overline{B}$

- c) Indicar a validade do circuito da figura 55:

Figura 55 - Teorema de De Morgan.

- 1. Verdadeiro

- 2. Falso

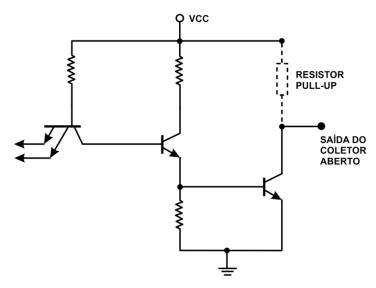

#### 1.8 GATES DE COLETOR ABERTO

#### **1.8.1 RESUMO**

O gate de Coletor Aberto é um CI que possui a característica especial de possuir o transistor de saída com o coletor disponível em um pino do CI, e desconectado de qualquer ligação interna, conforme mostra a figura 56.

Figura 56 - Circuito do gate de coletor abeto.

Para o funcionamento correto do gate há a necessidade da ligação de um resistor, denominado **Resistor** *Pull-up*, entre o coletor aberto e Vcc (mostrado na figura 56 em tracejado).

Este CI é apresentado assim a fim de permitir a implementação da Lógica por Fios (E por fios) e, deste modo, o resistor pull-up funciona como um regulador de corrente, sendo que seu valor vai depender do número de gates, que irão participar da conexão "E" por fios, e do número de cargas a serem alimentadas pelo ponto "E".

Existem também os **Buffers e Drivers** de coletor aberto, que diferem dos gates ordinários de coletor aberto por terem maior capacidade de absorção de corrente e um **Fan-Out** mais elevado: são usados na alimentação de cargas que exigem altas correntes.

Alguns destes circuitos têm a vantagem adicional de permitir a ligação do resistor pull-up em até 30V (como o 74LS06 e o 74LS07), podendo assim fazer interface de TTL para circuitos com tensão mais elevada que a dos gates TTL comuns.

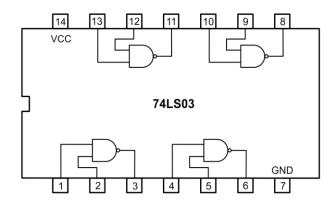

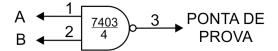

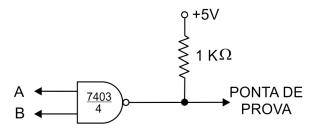

### 1.8.2 EXPERIÊNCIA 25

- a) Material utilizado: 1 x CI 74LS03, 1 resistor de 1K $\Omega$  e Ponta de Prova do equipamento.

- b) Layout do CI 74LS03.

Figura 57 - Layout do CI 74LS03.

c) Montar o circuito da figura 58

Figura 58 – Circuito para teste do gate de coletor aberto sem resistor pull-up.

d) Completar a tabela 29.

| ENTRADAS |   | SAÍDAS       |

|----------|---|--------------|

| Α        | В | Nível Lógico |

| Ø        | Ø |              |

| Ø        | 1 |              |

| 1        | 1 |              |

| 1        | Ø |              |

Tabela 29 – Tabela Verdade do gate de coletor aberto sem resistor pull-up.

# e) Montar o circuito da figura 59

Figura 59 – Gate de coletor aberto com o resistor pull-up.

f) Completar a tabela 30.

| ENTRADAS |   | SAÍDAS       |

|----------|---|--------------|

| Α        | В | Nível Lógico |

| Ø        | Ø |              |

| Ø        | 1 |              |

| 1        | 1 |              |

| 1        | Ø |              |

Tabela 30 – Tabela Verdade do gate de coletor aberto com o resistor pull-up

### **CONCLUSÃO:**

Observar que o funcionamento correto do gate se faz quando é feita a ligação do resistor de  $1K\Omega$ .

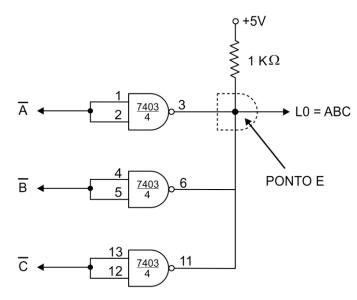

#### 1.8.3 EXPERIÊNCIA 26

- a) Material utilizado: 1 x Cl 74LS03, 1 resistor de 1KΩ

- **b)** Montar o circuito da figura 60.

Figura 60 – Lógica por fios usando Gates de coletor aberto.

## c) Completar a tabela 31

| ENTRADAS |   | AS | SAÍDAS         |

|----------|---|----|----------------|

| Α        | В | С  | L0 = A . B . C |

| Ø        | Ø | Ø  |                |

| Ø        | Ø | 1  |                |

| Ø        | 1 | Ø  |                |

| Ø        | 1 | 1  |                |

| 1        | Ø | Ø  |                |

| 1        | Ø | 1  |                |

| 1        | 1 | Ø  |                |

| 1        | 1 | 1  |                |

Tabela 31 – Tabela Verdade do circuito com Gates de coletor aberto executando lógica por fios.

### **CONCLUSÃO:**

No circuito montado o número de Gates envolvidos pode ser aumentado sem que haja dano nos Cl's. Como regra prática, para até 7 gates de entrada com um Fan-out de 7 usase um resistor de  $1K\Omega$ .

## MÓDULO 8810 – MANUAL TEÓRICO E PRÁTICO

# CAPÍTULO 1 - GATES LÓGICOS BÁSICOS

# 1.8.4 EXERCÍCIOS

| a) | O gate de coletor aberto:       |  |

|----|---------------------------------|--|

|    | 1. Permite a lógica por fios    |  |

|    | 2. Introduz atraso no sistema   |  |

|    | 3. É usado como Interface       |  |

| b) | O resistor pull-up serve:       |  |

| Í  | 1. Para quadrar a onda de saída |  |

|    | 2. Para evitar ruído            |  |

|    | 3. Para controle de corrente    |  |

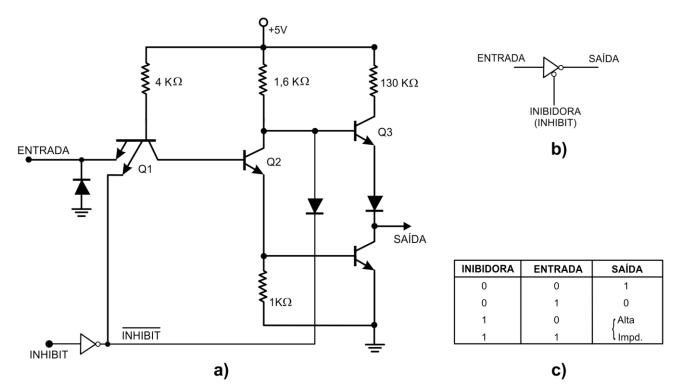

#### 1.9 GATES TRI-STATE

#### 1.9.1 **RESUMO**

O dispositivo denominado *Tri-State* é um circuito que permite três estados:

- 1. Estado lógico "1" (baixa impedância para VCC);

- 2. Estado lógico "0" (baixa impedância para terra);

- 3. Desligado (disabled) (apresenta alta impedância tanto para VCC como para terra).

Destes três estados, o que se apresenta como novidade é o terceiro (desligado). Neste estado o circuito se apresenta como se estivesse desconectado do resto do sistema, isto é, não há troca de corrente com os circuitos conectados a esta saída. Assim, quando está neste estado, sua saída não influência e nem é influenciada pelo sistema a ela conectada.

Os dispositivos *Tri-State* possuem uma entrada habilitadora / desabilitadora além das entradas e saídas normais.

Quando habilitado o gate funciona normalmente e quando desabilitado apresenta uma alta impedância de saída. A figura 61 ilustra o circuito do dispositivo *Tri-State* TTL.

Figura 61 – a) Circuito do dispositivo Tri-state – b) Símbolo - c) Tabela Verdade.

O circuito da figura 61, a) funciona da seguinte maneira: Quando a entrada **Inhibit** está em "0", faz com que o transistor de entrada (MET) e o diodo da base de **Q3** seja polarizadas reversamente, assim o circuito funciona como um inversor normal.

Porém quando **Inhibit** esta em "1", o fluxo de corrente na junção base-emissor de **Q1** deixa **Q2** sem corrente de base, levando-o ao corte e, consequentemente, **Q4** também. O diodo na base de **Q3** estará conduzindo e levando **Q3** ao corte.

Assim **Q3** e **Q4** estarão em corte, o que ocasiona uma saída de alta impedância tanto para VCC como para terra.

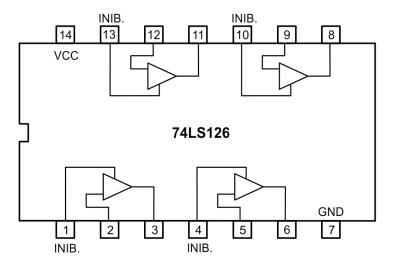

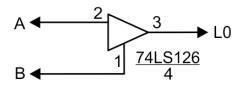

### 1.9.2 EXPERIÊNCIA 27

- a) Material utilizado: 1 x Cl 74LS126

- b) Layout do CI 74LS126.

Figura 62 - Layout do CI 74126.

c) Mostrar o circuito da figura 63

Figura 63 – Gate Tri-State.

### d) Completar a tabela 32

| ENTRADAS |           | SAÍDAS |

|----------|-----------|--------|

| DADOS    | INIBIDORA |        |

| Α        | В         | LO     |

| Ø        | Ø         |        |

| Ø        | 1         |        |

| 1        | 1         |        |

| 1        | Ø         |        |

Tabela 32 – Tabela Verdade do gate Tri-State

### **CONCLUSÃO:**

Observar que quando a entrada inibidora está em "0" (B=0) nada ocorre com a saída  $L_0$ , e para a entrada inibidora em "1" (B=1) a saída  $L_0$  segue o nível colocado em A. O uso da ponta de prova, ao invés de  $L_0$ , irá mostrar a operação do circuito *Tri-State* mais adequadamente. (A= aberto, quando B=0).

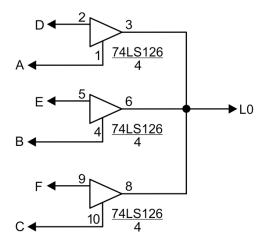

#### 1.9.3 EXPERIÊNCIA 28

- a) Material utilizado: 1 x CI 74LS126

- **b)** Montar o circuito da figura 64.

Figura 64 – Circuito de um barramento com Gates Tri-States.

### Observação:

O circuito do 74LS126 pode ser facilmente queimado. Somente uma das entradas inibidoras (ABC) pode estar no nível "1" de cada vez.

## c) Completar a tabela 33.

| ENTRADAS<br>INIBIDORAS |   | ENTRADAS DE<br>DADOS |   |   | SAÍDA |    |

|------------------------|---|----------------------|---|---|-------|----|

| Α                      | В | С                    | D | Е | F     | LØ |

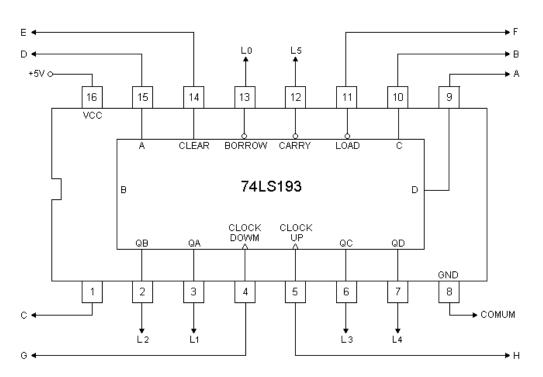

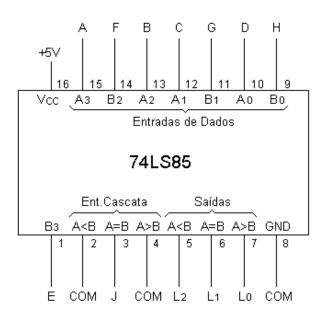

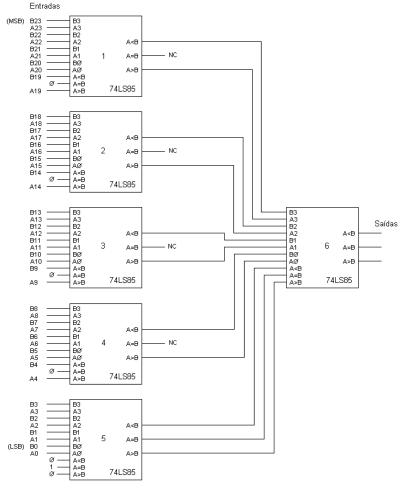

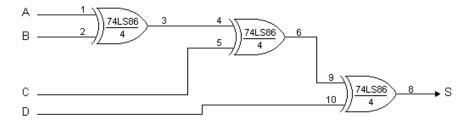

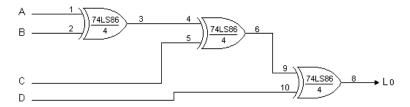

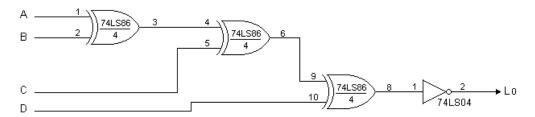

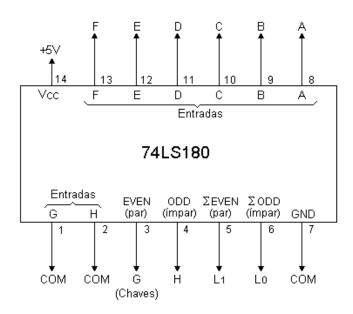

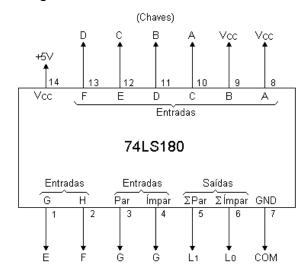

| 1                      | Ø | Ø                    | Ø | Ø | Ø     |    |